Cp390 hotswap – Kontron CP390 User Manual

Page 29

CP390

Hotswap

ID 19976, Rev. 0200

Page 4 - 7

® PEP Modular Computers GmbH

4.2.6

Programming the GPIO’s

This sub-chapter provides information for programming the GPIO’s (General Purpose

I/O’s) of the PCI-to-PCI bridge.

4.2.6.1 GPIO: Output Enable Control Register - Offset 66h

This section describes the GPIO for the Output Enable Control Register.

Dword address = 64h

Byte enable p_cbe_1<3:0> = x0xxb

4.2.6.2 GPIO Input Data Register - Offset 67h

This section describes the GPIO input data register.

Dword address = 64h

Byte enable p_cbe_1<3:0> = 0xxxb

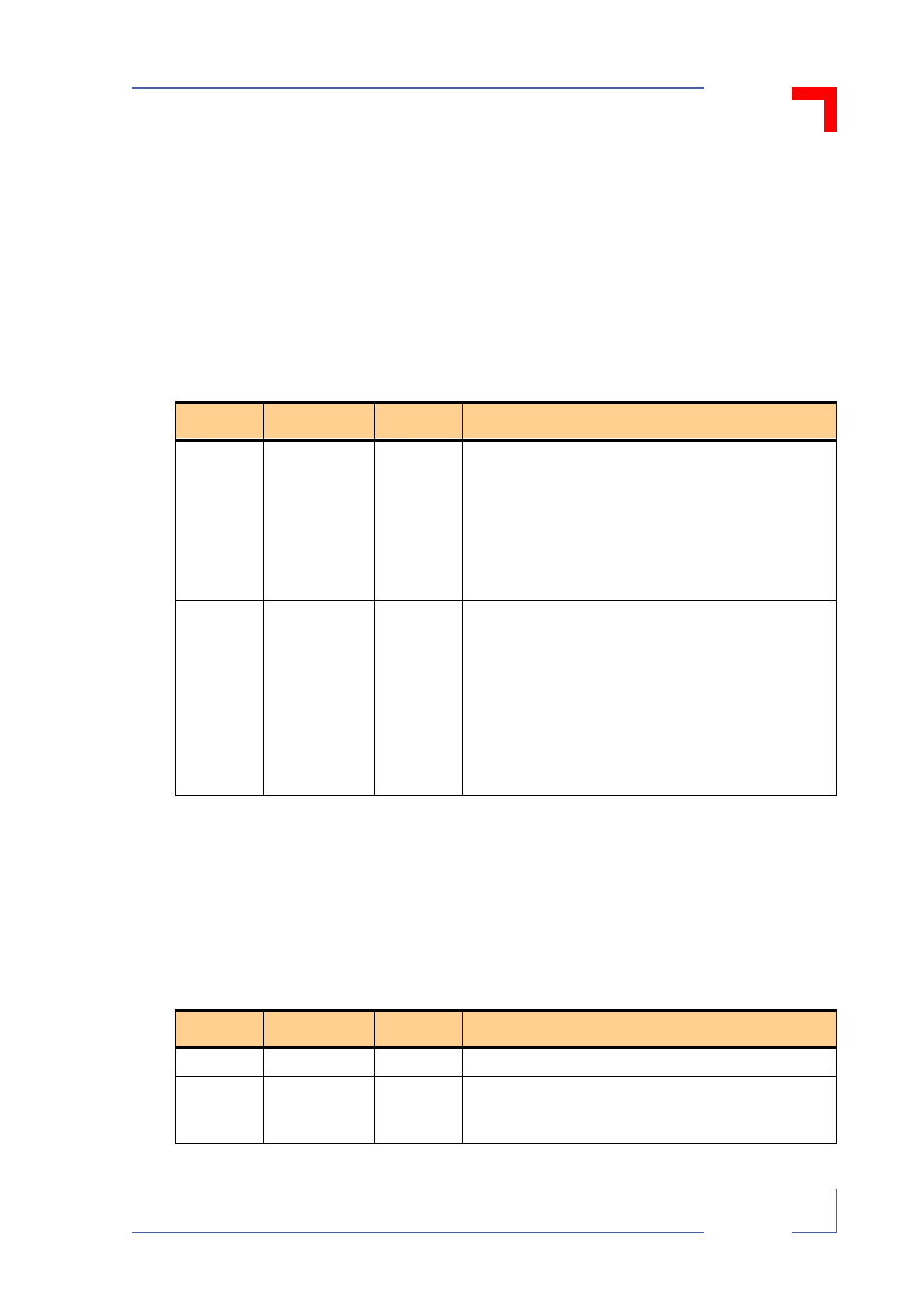

Table 4-3: GPIO Output Enable Control Gegister - Offset 66h

Dword Bit

Name

R/W

Description

19:16

GPIO output

enable

write-1-to-clear

R/W1TC

The gpio<3:0> output enable control

write-1-to-clear. Writing 1 to any of these bits config-

ures the corresponding gpio<3:0> pin as an input

only; that is, the output driver is tristated.

Writing 0 to this register has no effect.

When read, reflects the last value written.

Reset value: 0 (all pins are input only).

23:20

GPIO output

enable

write-1-to-set

R/W1TS

The gpio<3:0> output enable control

write-1-to-set. Writing 1 to any of these bits config-

ures the corresponding gpio<3:0> pin as bidirec-

tional, that is,

enables the output driver and drives the value set in

the output data register (65h).

Writing 0 to this register has no effect.

When read, reflects the last value written.

Reset value: 0 (all pins are input only).

Table 4-4: GPIO Input Data Register - Offset 67h

Dword Bit

Name

R/W

Description

27:24

Reserved

R

Reserved. Returns 0 when read.

31:28

GPIO input

R

This read-only register reads the state of the

gpio<3:0> pins. This state is updated on the

PCI clock cycle following a change in the gpio pins.