3 debouncing inputs, Debouncing inputs - 8, Input control register - 8 – Kontron CP381 User Manual

Page 50: Programmable input sample rates - 8, Configuration cp381

Configuration

CP381

Page 4 - 8

© 2002 PEP Modular Computers GmbH

ID 24107, Rev. 01

4.3.3

Debouncing Inputs

By default, all inputs are filtered through a passive analog low-pass filter placed immediately

behind the input connector. Additionally, the CP381 provides a programmable digital debounc-

er which is common for all inputs. It functions as follows; the input ports are sampled at a pro-

grammable sample rate which is derived from PCI bus clock. Two consecutive samples must

be equal before being stored in the input data register. By this means, bouncing and spikes on

inputs can be filtered out. For example, with a selected input sample rate of 500 Hz, input puls-

es which are shorter than 2 ms are filtered out.

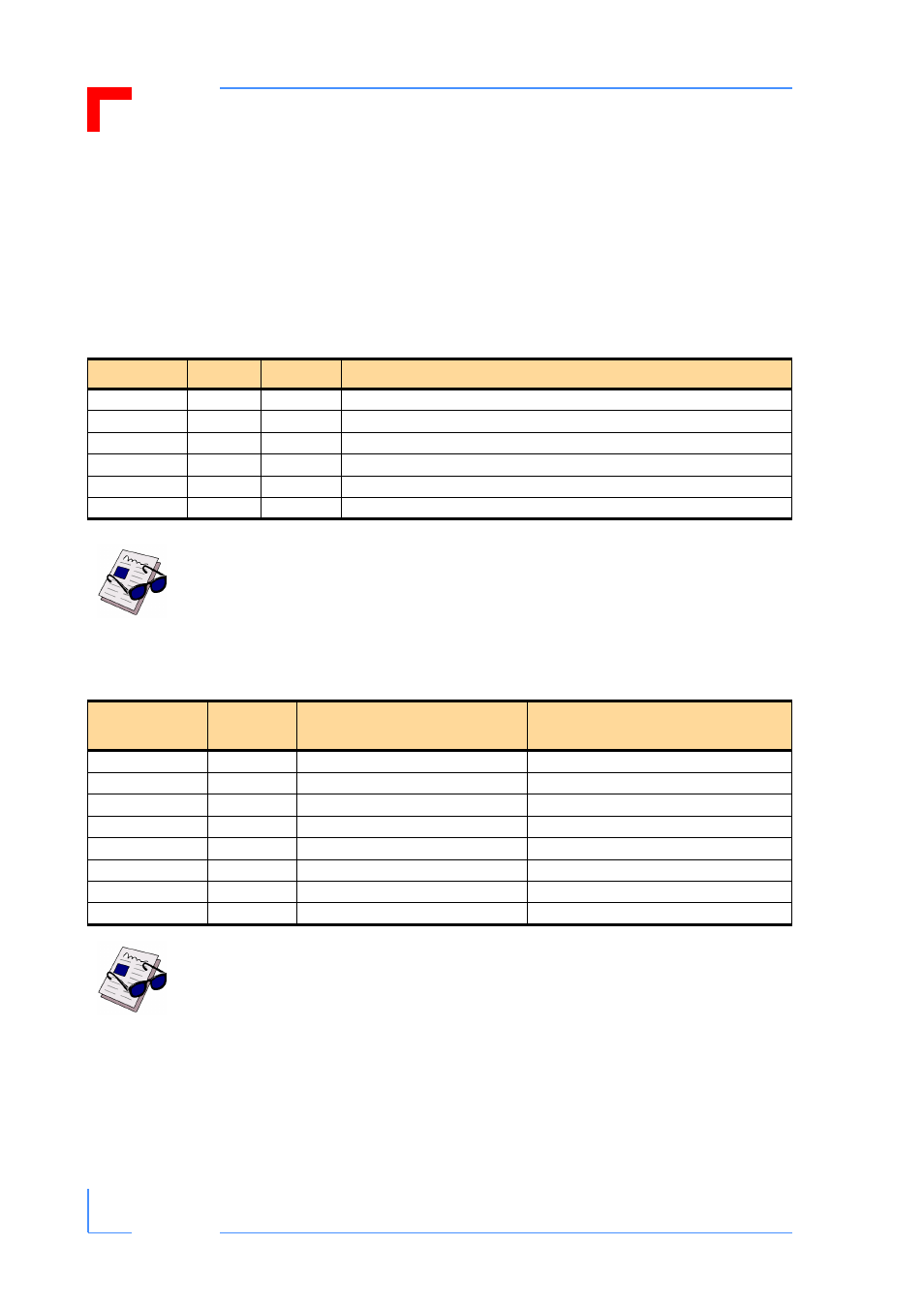

Table 4-4: Input Control Register

Bits

Type

Default

Function

31-8

r/w

0

Reserved

7

r/w

0

Input enable

6

r/w

0

Event detect enable

5

r/w

0

Latch mode enable

4

r/w

0

Pattern detect enable

2-0

r/w

000

Debounce control deb[2..0]

Note...

The Inputs are sampled through the debouncer after the Input Enable bit is set.

Additional features such as event and pattern detection and latch mode are also

enabled in the input control register, after being configured within the corre-

sponding mode registers.

Table 4-5: Programmable Input Sample Rates

deb[2..0]

Clock

Divider

Input Sample clock

@ 33MHz PCI

Input Sample period @ 33MHz PCI

000

1

33 MHz

30 ns

001

2^8

128 KHz

8 us

010

2^10

32 KHz

32 us

011

2^12

8 KHz

128 us

100

2^14

2 KHz

0.5 ms

101

2^16

0.5 KHz

2 ms

110

2^18

125 Hz

8 ms

111

2^20

31 Hz

32 ms

*Note...

The clock divider default value is 1. In addition to the choice of debouncing fil-

ters, there is an analog filter implemented on board with an edge frequency at

10 kHz.