Programming the dai for the 73xx, Digital audio clock generation – Cirrus Logic AN199 User Manual

Page 3

AN199Rev1

Copyright 2001 Cirrus Logic (All Rights Reserved)

3

AN199

Programming the DAI for the 73xx

The 73xx chips have been enhanced with a DAI interface which allows for MCLK to be clocked at 64Fs

(64 x sampling rate) as well as the traditional 128Fs provided by the 72xx series. There are CODECs on the market

that support 64Fs mode.

The sample rate is also programmable. This allows for greater flexibility in the code design for individual songs

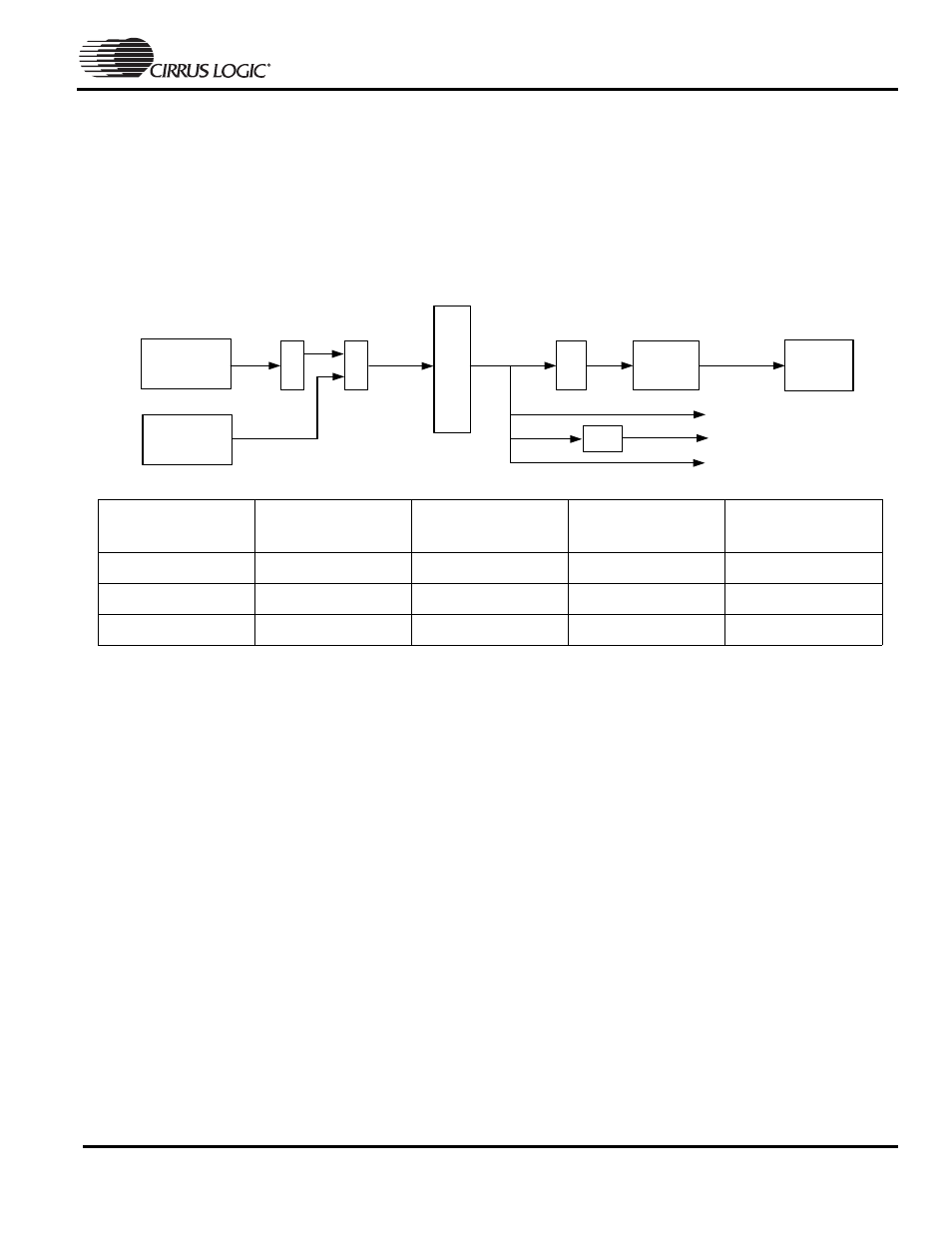

digitized and compressed at different rates. The diagram and table below illustrate the DAI control.

• Either 64Fs or 128Fs must be used for the 73XX. With one selected, the other must be turned off. For 128Fs,

SYSCON3 bit 9 will be set, and bit 0 of the DAI64Fs control register will be cleared. For 64Fs, the converse

must be applied.

• Register DAI64Fs must also be programmed to set the AUDCLKSRC, AUDIV, and to enable or disable 64Fs

mode. MCLK256EN will be enabled. Use the table above or refer to the 73xx User Manual for more detail.

• Settings for 8-24 kHz sample frequencies are not included. The side-effect of using a sample frequency

below 32 kHz is the raising of the noise floor at the external CODEC, thereby increasing the distortion of

the original signal. This issue is external to the processor. In order to decrease noise, samples that fall below

24 kHz sample rate should pass through a sample rate conversion in software to bring it up to a higher rate.

Conversion rates are as follows:

— 8 and 16 kHz to 32 kHz

— 11 and 22 kHz to 44.1 kHz

— 12 and 24 kHz to 48 kHz

Clock Source

(MHz)

Sample Frequency

(kHz)

128Fs Audio Bit Clock

(MHz)

64Fs Audio Bit Clock

(MHz)

128/64 Divisor

(AUDDIV)

73.728

32

4.0960

2.0480

9

11.2896

44.1

5.6448

2.8224

2

73.728

48

6.1440

3.0720

6

PLL

(73.728MHz)

EXTCLK

(11.2896)

/2

MUX

(AUDCLKSRC)

Programmable Divide

(AUDIV)

128/64(Fs)

/32

Audio Bit Clock 128/64(Fs)

SCLK

/128

/64

LRCLK(Fs)

MCLK (BUZ)

7-bit

counter

fixed at 4

Audio

Sample

Frequency

(Fs)

Audio Data

FIFO

Control

Digital Audio Clock

Generation