An74 – Cirrus Logic AN74 User Manual

Page 3

AN74

AN74Rev2

3

data-state where it waits until data is read from its

serial port. Read_register then calls receive_byte

three times and transfers three bytes of information

from the CS5525/6/9 to the 80C51. Similar to

transfer_byte, receive_byte acquires a byte one bit

at a time MSB first. When the transfer is complete,

the variables high_byte, mid_byte, and low_byte

contain the CS5525/6/9’s 24-bit gain register.

Acquire Conversion

To acquire a conversion the subroutine

acquire_conversion is called. To prevent from cor-

rupting the configuration register

acquire_conversion

first instructs the 80C51 to

save the contents of configuration register. This in-

formation is stored in the variable high_byte,

mid_byte and low_byte. Then, PF (Port Flag, the

fifth bit in the configuration register which is now

represented as bit five in the variable low-byte) is

masked to logic 1. When PF is set to logic 1, SDO’s

function is modified to fall to logic 0 signaling

when a conversion is complete and ready to acquire

(refer to Figure 5). After the PF is set,

acquire_conversion sends the command-byte

0xC0 to the converter instructing it to perform a

single conversion. From there, acquire_conversion

calls the subroutine toggle_sdo. Toggle_sdo is rou-

tine that polls P1.2 (SDO) until its logic level drops

to logic 0. After SDO falls, toggle_sdo pulses P1.3

(SCLK) eight times to clear the SDO signal flag.

After the SDO flag is cleared, the 80C51 reads the

conversion data word. Figure 6 depicts how 16-bit

and 20-bit conversion words are stored.

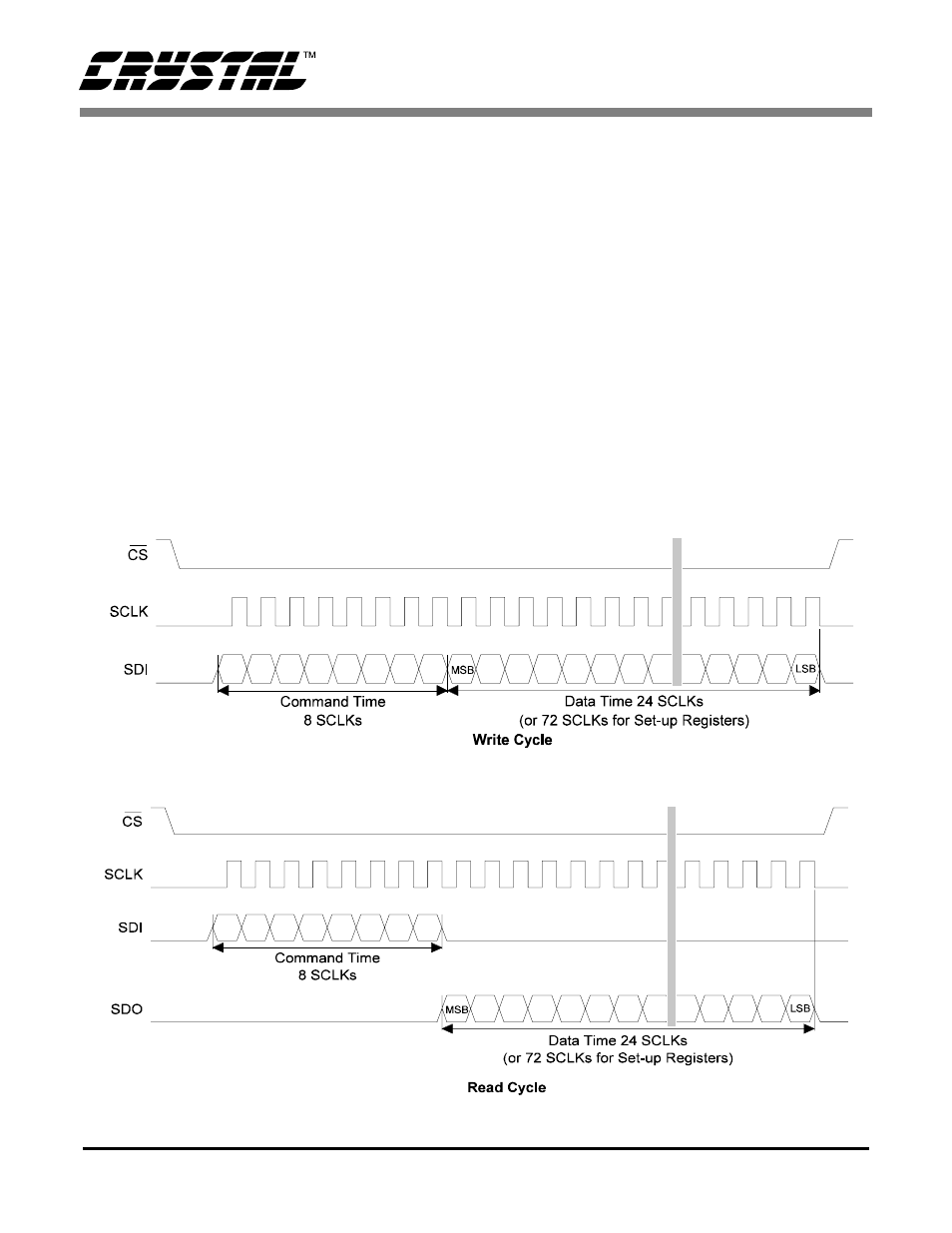

Figure 3. Write-Cycle Timing

Figure 4. Read-Cycle Timing