0 pin description - 8x interpolator mode, Master clock - mclk, Table 8. common clock frequencies – Cirrus Logic CS4397 User Manual

Page 24: Bit clock - bcki, Word clock - wcki, Serial audio data - dir and dil, Cs4397

CS4397

24

DS333F1

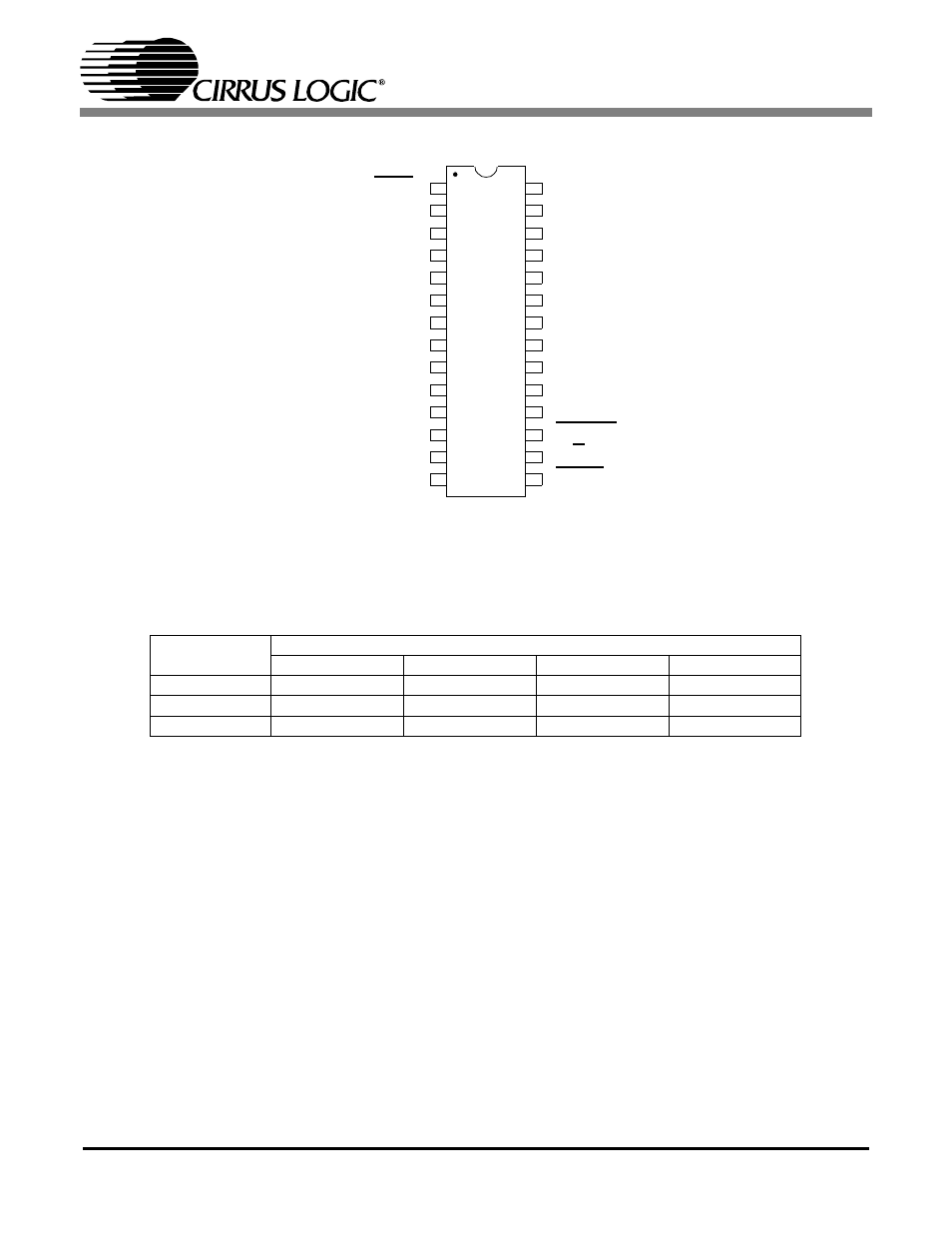

6.0 PIN DESCRIPTION - 8X INTERPOLATOR MODE

Master Clock - MCLK

Pin 10, Input

Function:

The master clock frequency must be either 32x, 48x, 64x or 96x the input sample rate. Table 8 illustrates

the standard audio sample rates and the required master clock frequencies.

Bit Clock - BCKI

Pin 11, Input

Function:

Clocks the individual serial data bits into the DIL and DIR pins. Refer to Figure 33

Word Clock - WCKI

Pin 12, Input

Function:

The word clock determines which channel is currently being input on the serial audio data input, SDATA.

The frequency of the word clock must be at 8x the baseband sample rate. Refer to Figure 33.

Serial Audio Data - DIR and DIL

Pins 12 and 13, Inputs

Function:

Two's complement MSB-first serial data is input on these pins. The data is clocked into DIL and DIR via

the bit clock. Refer to Figure 33.

Sample Rate

(kHz)

MCLK (MHz)

32x

48x

64x

96x

32 x 8

8.1920

12.2880

16.384

24.576

44.1 x 8

11.2896

16.9344

22.579

33.869

48 x 8

12.2880

18.4320

24.576

36.864

Table 8. Common Clock Frequencies

Refer to PCM mode RST

VREF

Refer to PCM mode

Refer to PCM mode M4(AD0/CS)

FILT+

Refer to PCM mode

Refer to PCM mode M3(AD1/CDIN)

FILT-

Refer to PCM mode

Refer to PCM mode M2(SCL/CCLK)

CMOUT

Refer to PCM mode

Refer to PCM mode M0(SDA/CDOUT)

AOUTL-

Refer to PCM mode

Refer to PCM mode DGND

AOUTL+

Refer to PCM mode

Refer to PCM mode VD

VA

Refer to PCM mode

Refer to PCM mode VD

AGND

Refer to PCM mode

Refer to PCM mode DGND

AOUTR+

Refer to PCM mode

Master Clock MCLK

AOUTR-

Refer to PCM mode

Bit Clock BCKI

AGND

Refer to PCM mode

Word Clock WCKI

MUTEC

Refer to PCM mode

Left Channel Data DIL

C/H

Refer to PCM mode

Right Channel Data DIR

MUTE

Refer to PCM mode

1

2

3

4

5

6

7

8

9

10

11

12

5

1

2

6

28

27

26

25

24

23

22

21

20

19

18

17

13

14

16

15