2 mode select, Table 5. mode selection, hardware mode options, Table 6 – Cirrus Logic CS4365 User Manual

Page 22: Cs4365

22

DS670F2

CS4365

4.2

Mode Select

In Hardware Mode, operation is determined by the Mode Select pins. The states of these pins are continu-

ally scanned for any changes; however, the mode should only be changed while the device is in reset

(RST pin low) to ensure proper switching from one mode to another. These pins require connection to sup-

ply or ground as outlined in

. For M0, M1, and M2, supply is VLC. For M3 and M4, supply is VLS.

show the decode of these pins.

In Software Mode, the operational mode and data format are set in the FM and DIF registers. See

Control (address 03h)” on page 35

.

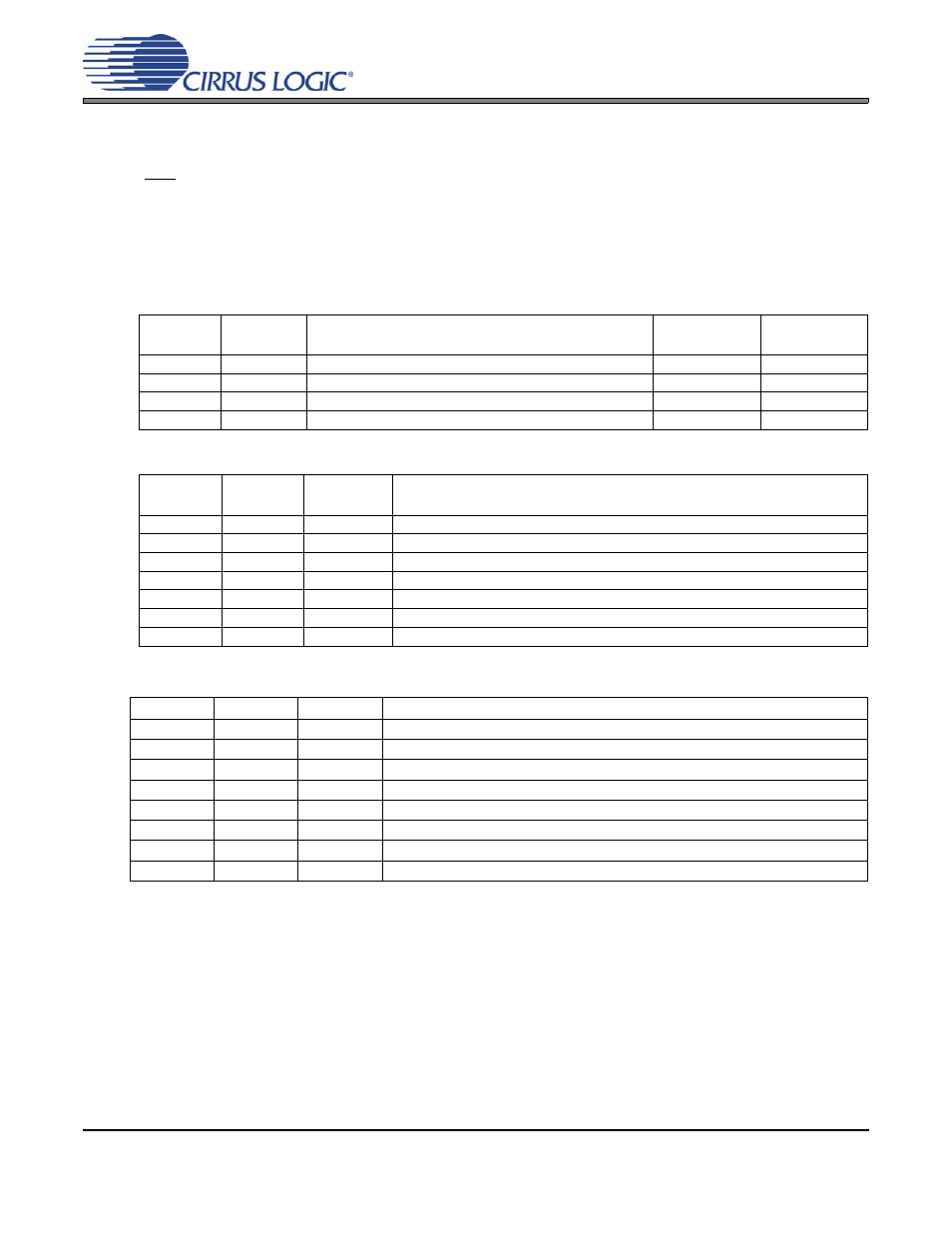

Table 4. PCM Digital Interface Format, Hardware Mode Options

M1

(DIF1)

M0

(DIF0)

DESCRIPTION

FORMAT

FIGURE

0

0

Left-Justified, up to 24-bit data

0

0

1

I²S, up to 24-bit data

1

1

0

Right-Justified, 16-bit Data

2

1

1

Right-Justified, 24-bit Data

3

M4

M3

M2

(DEM)

DESCRIPTION

0

0

0

Single-Speed without De-Emphasis (4 to 50 kHz sample rates)

0

0

1

Single-Speed with 44.1 kHz De-Emphasis; see

0

1

0

Double-Speed (50 to 100 kHz sample rates)

0

1

1

Quad-Speed (100 to 200 kHz sample rates)

1

0

0

Auto Speed-Mode Detect (32 kHz to 200 kHz sample rates)

1

0

1

Auto Speed-Mode Detect with 44.1 kHz De-Emphasis; see

1

1

X

for details)

Table 5. Mode Selection, Hardware Mode Options

M2

M1

M0

DESCRIPTION

0

0

0

64x oversampled DSD data with a 4x MCLK to DSD data rate

0

0

1

64x oversampled DSD data with a 6x MCLK to DSD data rate

0

1

0

64x oversampled DSD data with a 8x MCLK to DSD data rate

0

1

1

64x oversampled DSD data with a 12x MCLK to DSD data rate

1

0

0

128x oversampled DSD data with a 2x MCLK to DSD data rate

1

0

1

128x oversampled DSD data with a 3x MCLK to DSD data rate

1

1

0

128x oversampled DSD data with a 4x MCLK to DSD data rate

1

1

1

128x oversampled DSD data with a 6x MCLK to DSD data rate

Table 6. Direct Stream Digital (DSD), Hardware Mode Options