8 cpld, 9 db-25 computer parallel port, 10 external control header – Cirrus Logic CDB42428 User Manual

Page 6: 11 dsp header, 12 led function indicator, 13 power, 14 grounding and power supply decoupling, Table 1. system connections

CDB42428

6

1.8

CPLD

The CPLD controls the on-board signal routing and configuration (see Figure 14). The CPLD interfaces with the

computer software through the DB-25 parallel port header, or can communicate with an external processor via the

External Control header.

1.9

DB-25 Computer Parallel Port

On-board clock and data routing and configuration logic, as well as the CS424xx part are configured using a com-

puter with the supplied Windows®-based software. The software communicates via the DB-25 parallel port interface

(see Figure 13) to a local CPLD that can configure all parts on the board.

1.10

External Control Header

A 26-pin dual-row header allows access to the control signals needed to configure the CS424xx. The external con-

troller has access to the CS424xx I

2

C/SPI signals, master mute and reset, and the CS424xx interrupt signal is avail-

able (see Figure 13). All control header signals are buffered, and are referenced to VLC levels. See Table 3 for a

complete description of External Control Header signals.

1.11

DSP Header

A 32-pin dual-row header provides access to the serial audio signals required to interface with a DSP (see Figure 4).

Either the CS42428 (using the PLL recovered from the input ADC_LRCK or the OMCK oscillator), the CS8416 or

the DSP header can be the master of the MCLK signal. The CS8416 can supply the DSP header with its recovered

master clock (RMCK), or pass the local oscillator-sourced OMCK (of the CS8416).

The CS424xx ADC and DAC ports are individually selectable to be master or slave, and should source/receive their

clocks to/from the DSP as required. All serial port timings must be synchronous to the CS424xx OMCK or RMCK -

whichever is used to clock the codec. See the data sheet for a complete description of serial port modes of operation.

All DSP header signals are buffered, and are referenced to VLS levels. DSP interface power VLS and ground are

supplied to the header. See Table 4 for a complete description of DSP Header signals.

1.12

LED Function Indicator

D1 (see Figure 13) indicates that a master reset condition has occurred on the board. D4 (see Figure 14) is sourced

from the CPLD and is currently unsupported.

1.13

Power

Power can easily be supplied to the evaluation board through three binding posts, all referenced to the single black

binding post ground connector (see Figure 15).

Supply +18.0 VDC to the green binding post to provide the positive analog rail. Supply -18.0 VDC to the yellow bind-

ing post to provide the negative analog rail. +18 V and -18 V supply power to the op-amps and can be +/-12 to +/-

18 volts (must be +/-18 V when filter 2 is selected).

Supply +5.0 VDC to the red binding post. This directly supplies the digital +5 V, is regulated down to provide the

digital +3.3 V, and is filtered to supply VLC, and VA.

VLS and VD must be individually set with jumpers to either +3.3 V or +5 V.

1.14

Grounding and Power Supply Decoupling

The CS424xx requires careful attention to power supply and grounding arrangements to optimize performance.

Figures 18 and 19 detail the routing and component placement for both top and bottom layers of the demonstration

board. Power supply decoupling capacitors are located as close to the CS424xx as possible. Extensive use of

ground plane fill in the demonstration board yields large reductions in radiated noise.

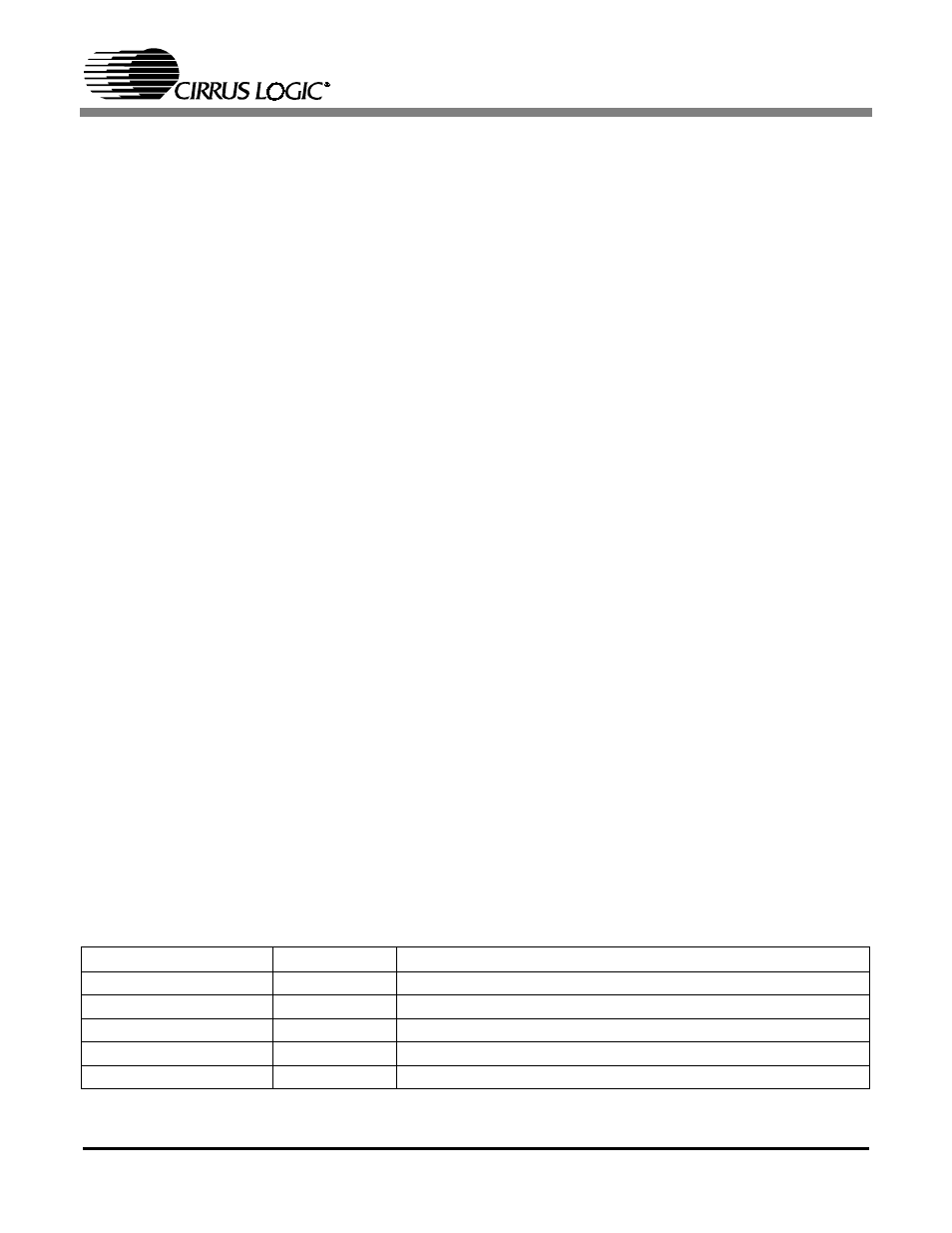

CONNECTOR

INPUT/OUTPUT

SIGNAL PRESENT

+5V

Input

+ 5VDC power

-18V

Input

-18 to -12 VDC negative supply for the op-amps

+18V

Input

+12 to +18 VDC positive supply for the op-amps

GND

Input

Ground connection from power supply

J39

Input

CS8416 digital audio interface input via coax

Table 1. System Connections