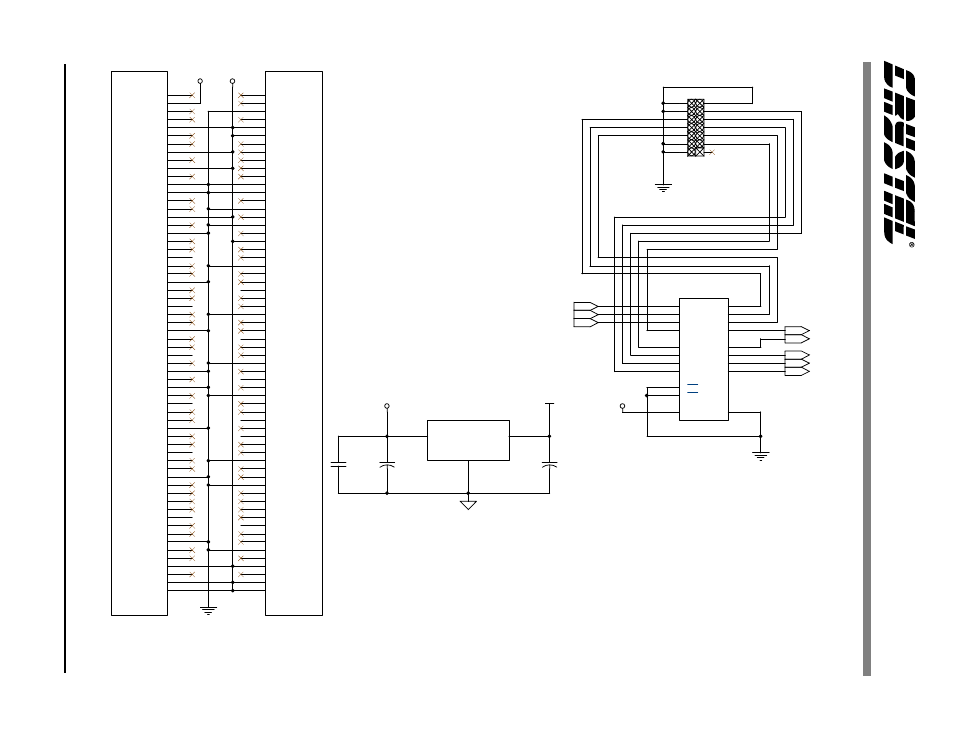

Figure 4. pci bus – Cirrus Logic CRD4205-2 User Manual

Page 9

C

RD4205-2

DS4

89R

D2A1

9

DS MicIn

DS CDIn

DS

LineIn

/OBE

DSMCK

DSLRCK

DSSCK

SDATA1

SDATA2

n.c.

(reserved)

To Main

Board

+12VD

+12VD

DGND

+5VD

AGND

+5VA

DGND

DGND

+5VD

7 4 H C 2 4 4

U 9

3

5

7

9

12

14

16

18

17

15

13

11

8

6

4

2

20

19

10

1

2 Y 4

2 Y 3

2 Y 2

2 Y 1

1 Y 4

1 Y 3

1 Y 2

1 Y 1

2 A 4

2 A 3

2 A 2

2 A 1

1 A 4

1 A 3

1 A 2

1 A 1

V C C

2 O E

G N D

1 O E

J 1 4

7 x 2 C O N

1

2

3

4

5

6

7

8

9

10

11

12

13

14

+

C 4 3

1 0 u F

E L E C

U 8

M C 7 8 M 0 5 C

3

2

1

O U T

G N D

IN

C 4 1

0.1uF

Z 5 U

+

C 4 2

1 0 u F

E L E C

Side B

P 1

PCI BUS 5V B

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

-12V

T C K

G N D 1 1

T D O

+5V(8)

+5V(9)

I N T B #

I N T D #

P R S N T 1 #

R S V D ( 4 )

P R S N T 2 #

G N D ( 1 2 )

G N D ( 1 3 )

R S V D ( 5 )

G N D ( 1 4 )

C L K

G N D ( 1 5 )

R E Q #

+5V(10)

AD[31]

AD[29]

G N D ( 1 6 )

AD[27]

AD[25]

+3.3V(7)

C/BE[3]#

AD[23]

G N D ( 1 7 )

AD[21]

AD[19]

+3.3V(8)

AD[17]

C/BE[2]#

G N D ( 1 8 )

IRDY#

+3.3V(9)

D E V S E L #

G N D ( 1 9 )

L O C K #

P E R R #

+3.3V(10)

S E R R #

+3.3V(11)

C/BE[1]#

AD[14]

G N D ( 2 0 )

AD[12]

AD[10]

G N D ( 2 1 )

K E Y 3

K E Y 4

AD[8]

AD[7]

+3.3V(12)

AD[5]

AD[3]

G N D ( 2 2 )

AD[1]

+5V(11)

A C K 6 4 #

+5V(12)

+5V(13)

Side A

P 2

PCI BUS 5V A

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

T R S T #

+ 1 2 V

T M S

T D I

+5V(1)

I N T A #

I N T C #

+5V(2)

R S V D ( 1 )

+5V(3)

R S V D ( 2 )

G N D ( 1 )

G N D ( 2 )

R S V D ( 3 )

R S T #

+5V(4)

G N T #

G N D ( 3 )

P M E #

AD[30]

+3.3V(1)

AD[28]

AD[26]

G N D ( 4 )

AD[24]

IDSEL

+3.3V(2)

AD[22]

AD[20]

G N D ( 5 )

AD[18]

AD[16]

+3.3V(3)

F R A M E #

G N D ( 6 )

T R D Y #

G N D ( 7 )

S T O P #

+3.3V(4)

S D O N E

S B O #

G N D ( 8 )

P A R

AD[15]

+3.3V(5)

AD[13]

AD[11]

G N D ( 9 )

AD[9]

K E Y 1

K E Y 2

C/BE[0]#

+3.3V(6)

AD[6]

AD[4]

G N D ( 1 0 )

AD[2]

AD[0]

+5V(5)

R E Q 6 4 #

+5V(6)

+5V(7)

D S S D I 3

D S S D I 2

S D A T A 2

D S M C K

D S S C K

D S S D I 1

D S L R C K

S D A T A 1

Figure 4. PCI Bus