4 global configuration (address 05h), 1 device configuration freeze (freeze), 5 ratio (address 06h - 09h) – Cirrus Logic CS2200-CP User Manual

Page 21: P 21, Cs2200-cp, Device configuration freeze (freeze)

CS2200-CP

DS759F2

21

8.3.3

Enable Device Configuration Registers 1 (EnDevCfg1)

This bit, in conjunction with EnDevCfg2, configures the device for control port mode. These EnDevCfg

bits can be set in any order and at any time during the control port access sequence, however they must

both be set before normal operation can occur.

Note:

EnDevCfg2 must also be set to enable control port mode. See

.

8.4

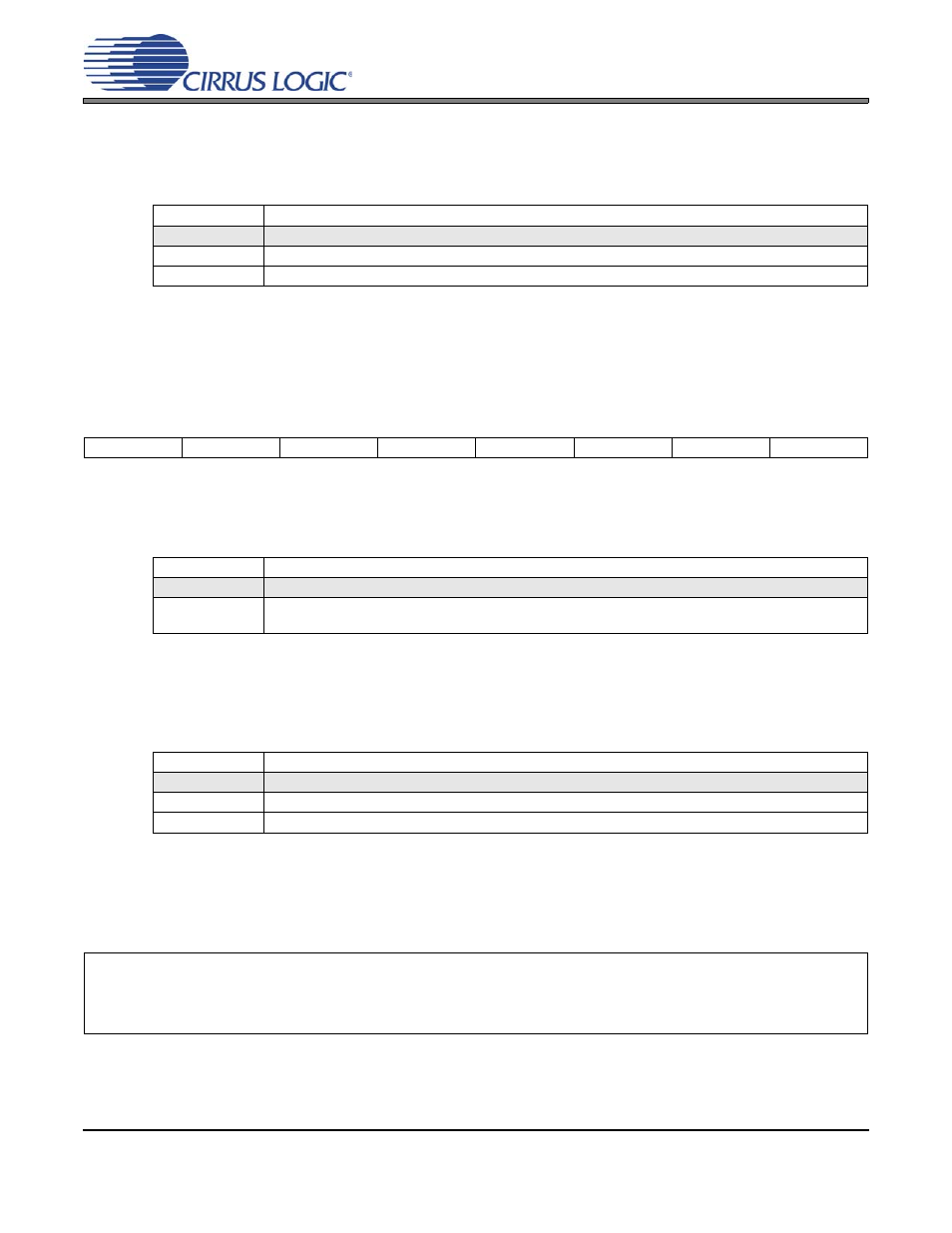

Global Configuration (Address 05h)

8.4.1

Device Configuration Freeze (Freeze)

Setting this bit allows writes to the Device Control and Device Configuration registers (address 02h - 04h)

but keeps them from taking effect until this bit is cleared.

8.4.2

Enable Device Configuration Registers 2 (EnDevCfg2)

This bit, in conjunction with EnDevCfg1, configures the device for control port mode. These EnDevCfg

bits can be set in any order and at any time during the control port access sequence, however they must

both be set before normal operation can occur.

Note:

EnDevCfg1 must also be set to enable control port mode. See

.

8.5

Ratio (Address 06h - 09h)

These registers contain the User Defined Ratio as shown in the

“Register Quick Reference” section on

. These 4 registers form a single 32-bit ratio value as shown above. See

Ratio Configuration” on page 12

“Calculating the User Defined Ratio” on page 23

for more details.

EnDevCfg1

Register State

0

Disabled.

1

Enabled.

Application:

“SPI / I²C Control Port” on page 16

7

6

5

4

3

2

1

0

Reserved

Reserved

Reserved

Reserved

Freeze

Reserved

Reserved

EnDevCfg2

FREEZE

Device Control and Configuration Registers

0

Register changes take effect immediately.

1

Modifications may be made to Device Control and Device Configuration registers (registers 02h-04h) without

the changes taking effect until after the FREEZE bit is cleared.

EnDevCfg2

Register State

0

Disabled.

1

Enabled.

Application:

“SPI / I²C Control Port” on page 16

7

6

5

4

3

2

1

0

MSB

............................................................................................................................

MSB-7

MSB-8

............................................................................................................................

MSB-15

LSB+15

............................................................................................................................

LSB+8

LSB+7

............................................................................................................................

LSB