Cirrus Logic CS2200-CP User Manual

Cs2200-cp, Fractional-n frequency synthesizer, Features

Copyright

Cirrus Logic, Inc. 2010

(All Rights Reserved)

Fractional-N Frequency Synthesizer

Features

Delta-Sigma Fractional-N Frequency Synthesis

–

Generates a Low Jitter 6 - 75 MHz Clock

from an 8 - 75 MHz Reference Clock

Highly Accurate PLL Multiplication Factor

–

Maximum Error Less Than 1 PPM

I²C™ / SPI™ Control Port

Configurable Auxiliary Output

–

Buffered Reference Clock

–

PLL Lock Indication

–

Duplicate PLL Output

Flexible Sourcing of Reference Clock

–

External Oscillator or Clock Source

–

Supports Inexpensive Local Crystal

Minimal Board Space Required

–

No External Analog Loop-filter

Components

General Description

The CS2200-CP is an extremely versatile system clock-

ing device that utilizes a programmable phase lock loop.

The CS2200-CP is based on an analog PLL architec-

ture comprised of a Delta-Sigma Fractional-N

Frequency Synthesizer. This architecture allows for fre-

quency synthesis and clock generation from a stable

reference clock.

The CS2200-CP supports both I²C and SPI for full soft-

ware control.

The CS2200-CP is available in a 10-pin MSOP package

in Commercial (-10°C to +70°C) and Automotive (-40°C

to +85°C) grades.

Customer development kits are also available for device

evaluation. Please see

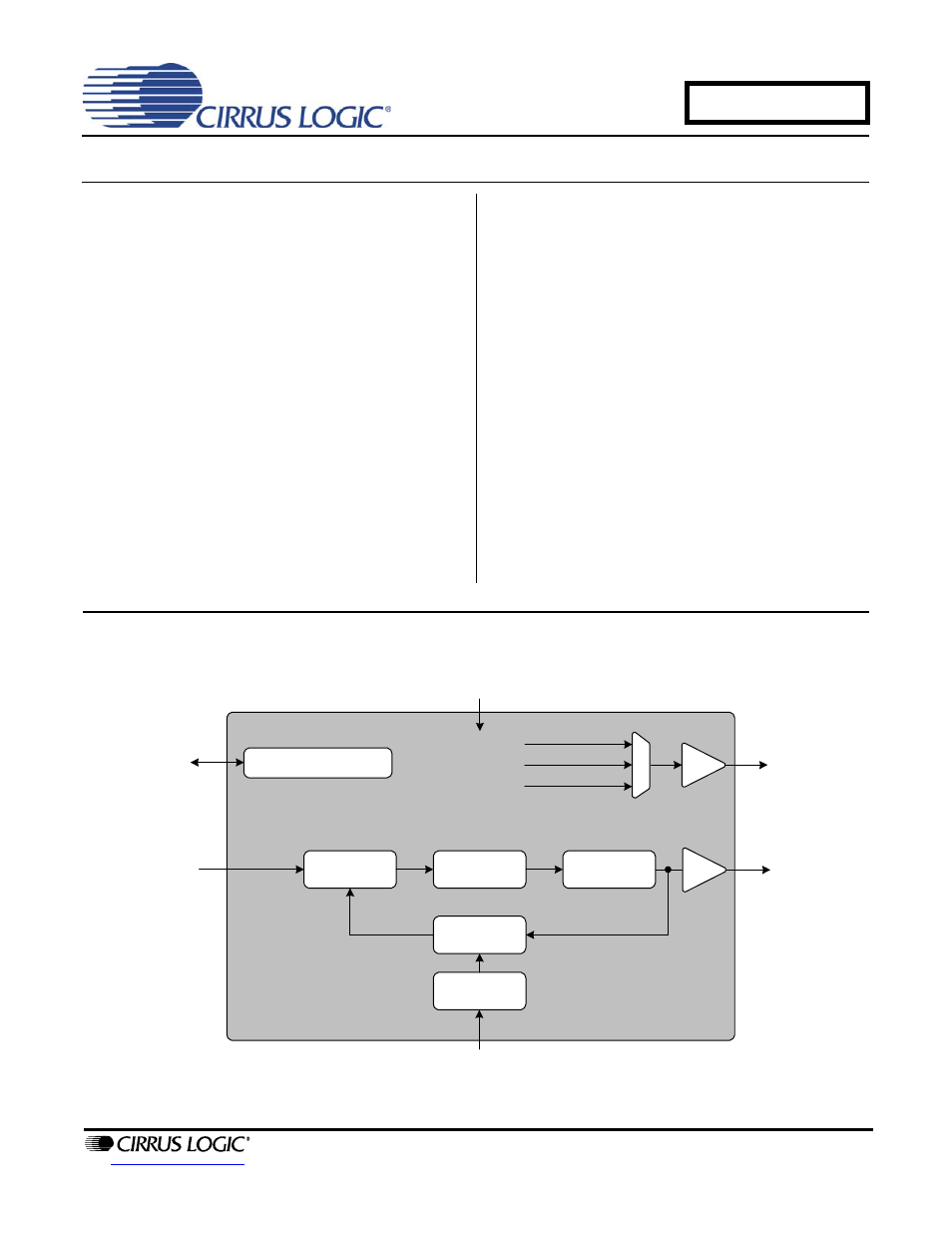

I²C / SPI

Auxiliary

Output

6 to 75 MHz

PLL Output

3.3 V

I²C/SPI Software

Control

8 MHz to 75 MHz

Low-Jitter Timing

Reference

Output to Input

Clock Ratio

N

Timing Reference

PLL Output

PLL Lock Indicator

Fractional-N

Divider

Voltage Controlled

Oscillator

Internal

Loop Filter

Phase

Comparator

Delta-Sigma

Modulator

MAY '10

DS759F2

CS2200-CP

Document Outline

- 1. Pin Description

- 2. Typical Connection Diagram

- 3. Characteristics and Specifications

- 4. Architecture Overview

- 5. Applications

- 6. SPI / I·C Control Port

- 7. Register Quick Reference

- 8. Register Descriptions

- 9. Calculating the User Defined Ratio

- 10. Package Dimensions

- 11. Ordering Information

- 12. References

- 13. Revision History