Pll performance plots, Figure 2. clk_in sinusoidal jitter tolerance, Figure 3. clk_in sinusoidal jitter transfer – Cirrus Logic CS2000-OTP User Manual

Page 8: Cs2000-otp, 25 °c; c, 15 pf; f, 288 mhz; f

CS2000-OTP

8

DS758F2

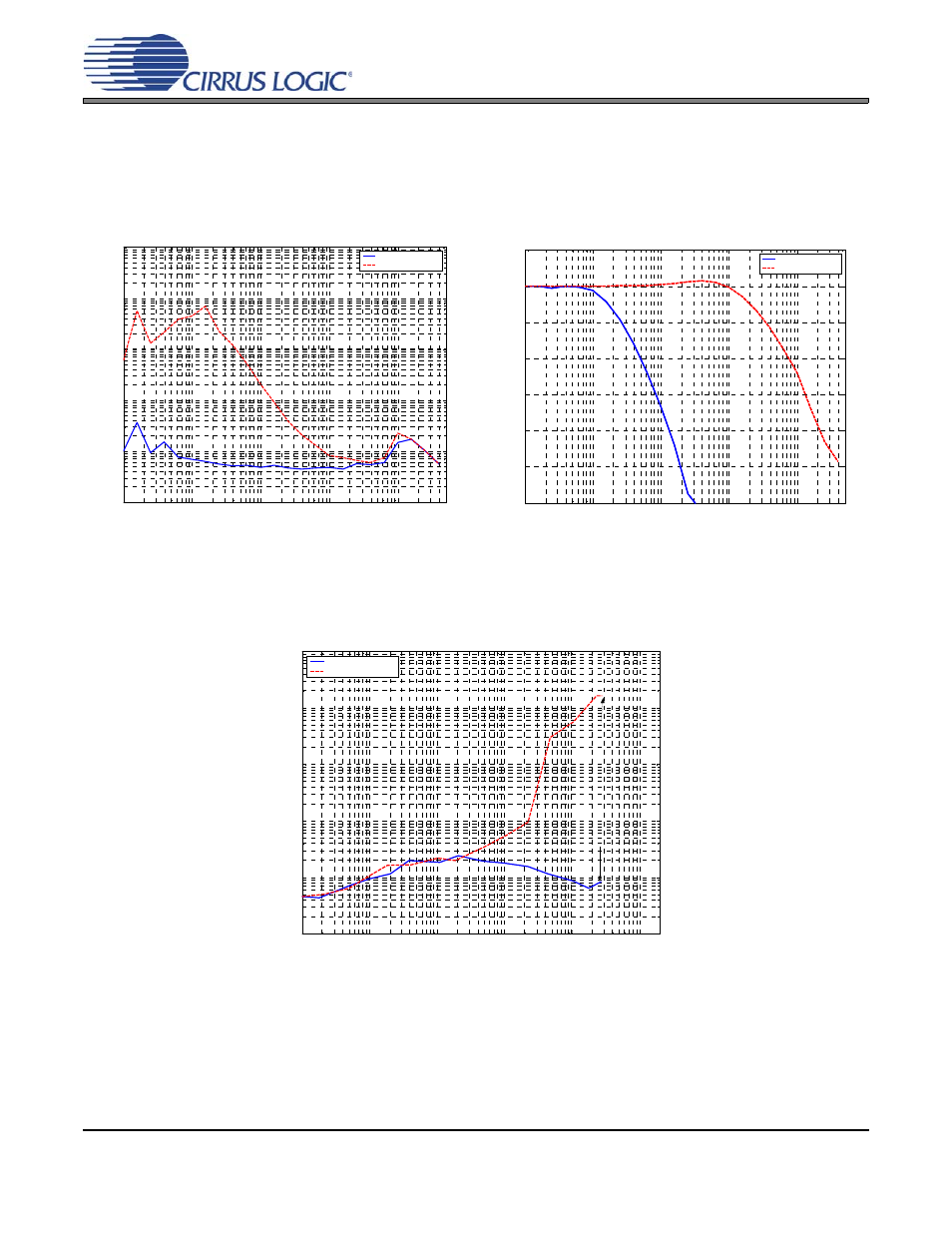

PLL PERFORMANCE PLOTS

Test Conditions (unless otherwise specified): VD = 3.3 V; T

A

= 25 °C; C

L

= 15 pF; f

CLK_OUT

= 12.288 MHz;

f

CLK_IN

= 12.288 MHz; Sample size = 10,000 points; Base Band Jitter (100 Hz to 40 kHz); AuxOutSrc[1:0] = 11.

1

10

100

1,000

10,000

0.1

1

10

100

1,000

10,000

Input Jitter Frequency (Hz)

M

a

x

In

p

u

t J

itte

r

L

e

v

e

l

(u

s

e

c

)

1 Hz Bandwidth

128 Hz Bandwidth

1

10

100

1000

10000

-60

-50

-40

-30

-20

-10

0

10

Input Jitter Frequency (Hz)

J

it

te

r Tr

an

sf

er

(

d

B)

1 Hz Bandwidth

128 Hz Bandwidth

Figure 2. CLK_IN Sinusoidal Jitter Tolerance

Figure 3. CLK_IN Sinusoidal Jitter Transfer

Samples size = 2.5M points; Base Band Jitter (10Hz to 40kHz).

Samples size = 2.5M points; Base Band Jitter (10Hz to 40kHz).

Figure 4. CLK_IN Random Jitter Rejection and Tolerance

0.01

0.1

1

10

100

1000

0.01

0.1

1

10

100

1000

Input Jitter Level (nsec)

O

u

tput

Ji

tt

e

r Level

(

n

sec)

1 Hz Bandwidth

128 Hz Bandwidth

Unlock

Unlock