3 lock clock ratio (lockclk[1:0]), 2 ratio 0 - 3, Cs2000-otp – Cirrus Logic CS2000-OTP User Manual

Page 23

CS2000-OTP

DS758F2

23

6.1.2

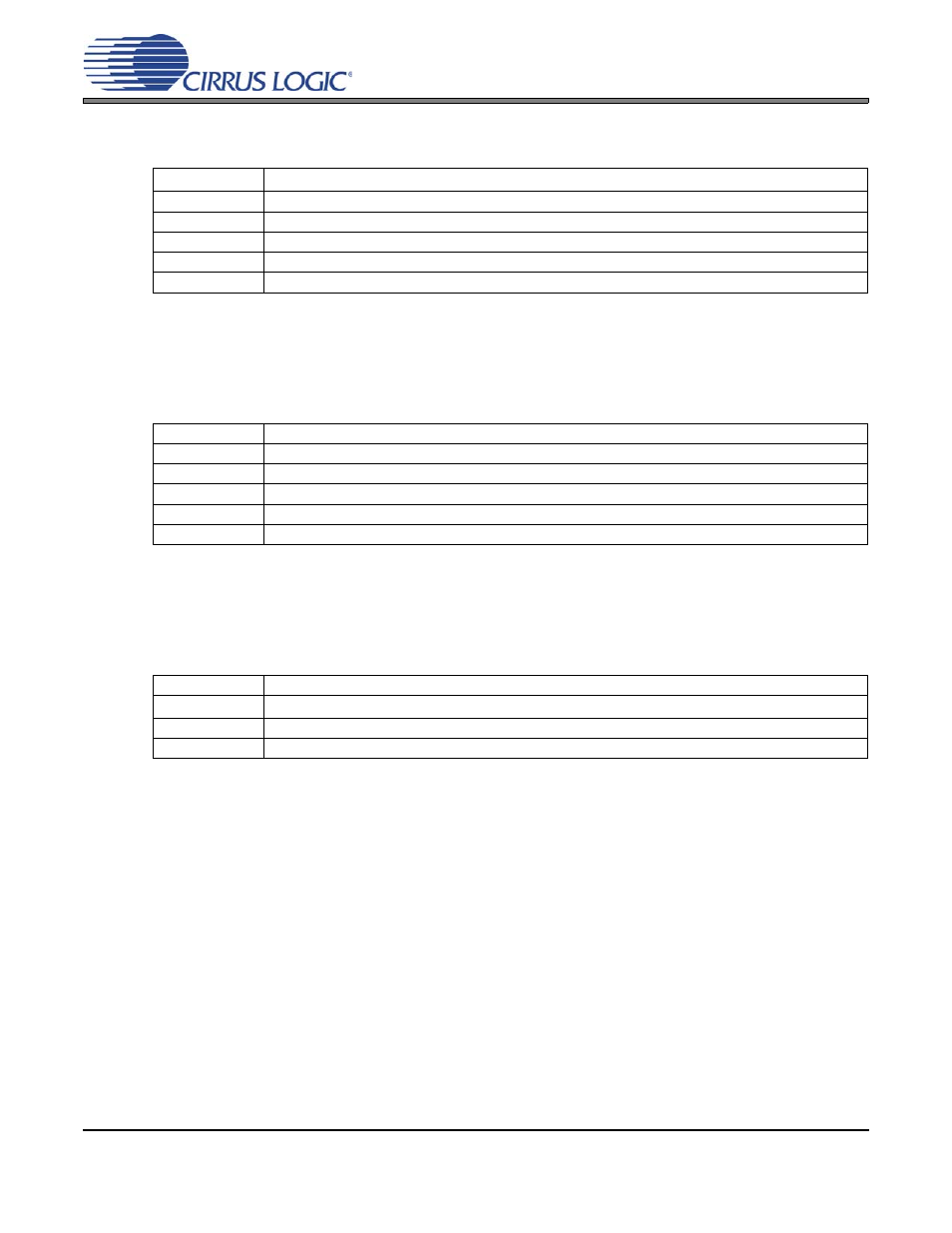

Auxiliary Output Source Selection (AuxOutSrc[1:0])

Selects the source of the AUX_OUT signal.

Note:

When set to 11, the AuxLockCfg global parameter sets the polarity and driver type (

Lock Output Configuration (AuxLockCfg)” on page 24

).

6.1.3

Lock Clock Ratio (LockClk[1:0])

Selects one of the four stored User Defined Ratios for use in the dynamic ratio based Hybrid PLL Mode.

Note:

The User Defined Ratio for the static ratio based Frequency Synthesizer mode is the ratio that

corresponds with the currently chosen configuration set as shown in

.

6.1.4

Fractional-N Source for Frequency Synthesizer (FracNSrc)

Selects static or dynamic ratio mode when auto clock switching is disabled.

6.2

Ratio 0 - 3

The four 32-bit User Defined Ratios are stored in the CS2000’s one time programmable memory. See

put to Input Frequency Ratio Configuration” on page 14

and

“Calculating the User Defined Ratio” on

for more details.

AuxOutSrc[1:0]

Auxiliary Output Source

00

RefClk.

01

CLK_IN.

10

CLK_OUT.

11

PLL Lock Status Indicator.

Application:

LockClk[1:0]

CLK_IN Ratio Selection

00

Ratio 0.

01

Ratio 1.

10

Ratio 2.

11

Ratio 3.

Application:

FracNSrc

Fractional-N Source Selection

0

Static Ratio directly from R

EFF

for Frequency Synthesizer Mode

1

Dynamic Ratio from Digital PLL for Hybrid PLL Mode

Application: