Figure 5-1: spi port full timing sequence, Figure 5-2: spi port timing parameters – PNI MicroMag User Manual

Page 20

PNI Sensor Corporation

DOC# 1015175 r01

MicroMag User Manual

– March 2010

Page 20 of 23

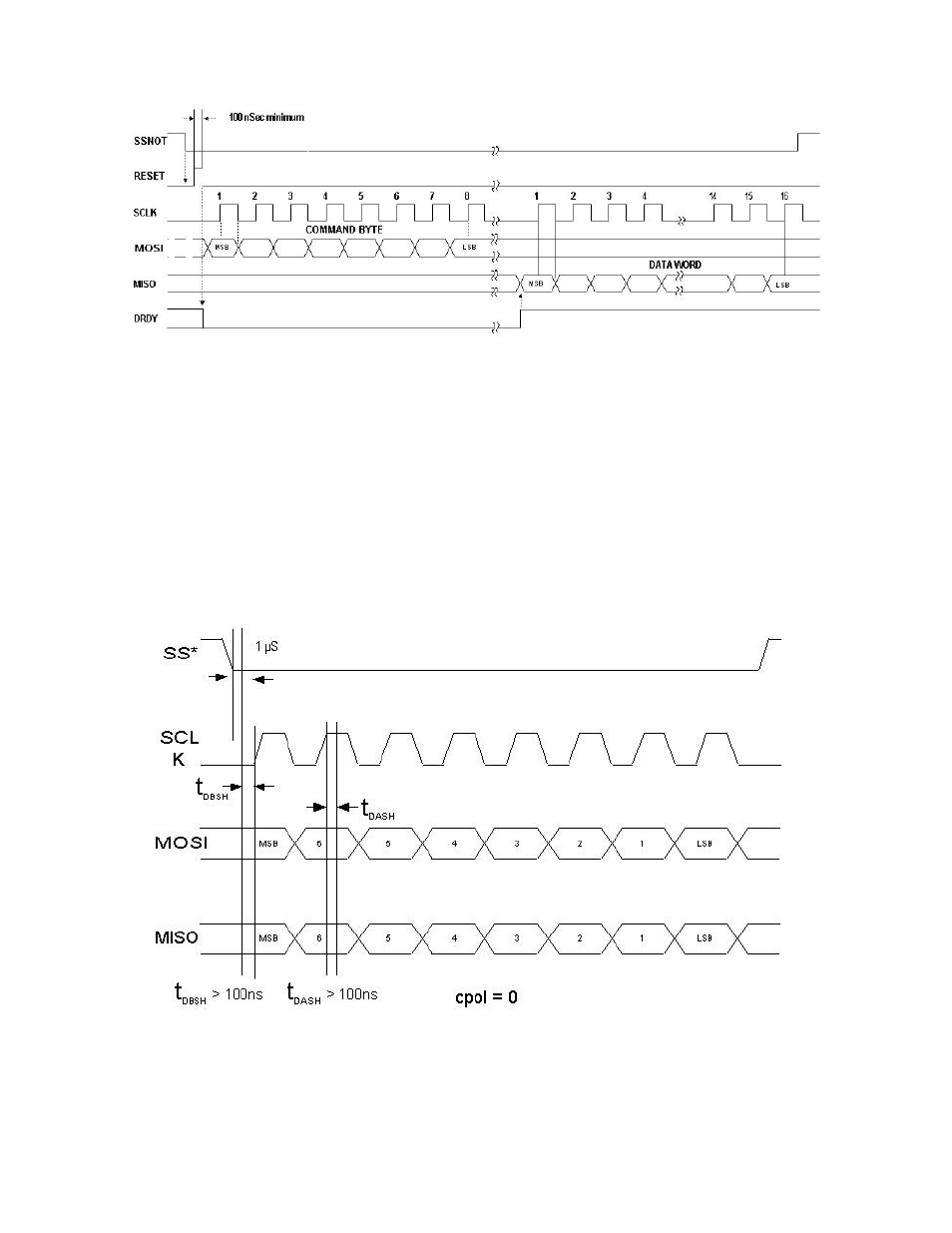

Figure 5-1: SPI Port Full Timing Sequence

When implementing an SPI port, whether it is a dedicated hardware peripheral port

or a software implemented port using general purpose I/O (also known as bit-banging)

the timing parameters given in Figure 5-2 must be met to ensure reliable

communications. Data is always considered valid while SCLK is HIGH (tDASH = Time,

Data After SCLK High). When SCLK is LOW, data is in transition (tDBSH = Time, Data

Before SCLK High).The clock set-up and hold times, t

DBSH

and t

DASH

must be greater

than 100 ns.

Figure 5-2: SPI Port Timing Parameters