D.1 a, Ddress, D.2 1 – IEI Integration PCIE-Q350 v1.00 User Manual

Page 242: Mb m, Emory, D.1 address map

PCIE-Q350 PICMG 1.3 CPU Card

Page 220

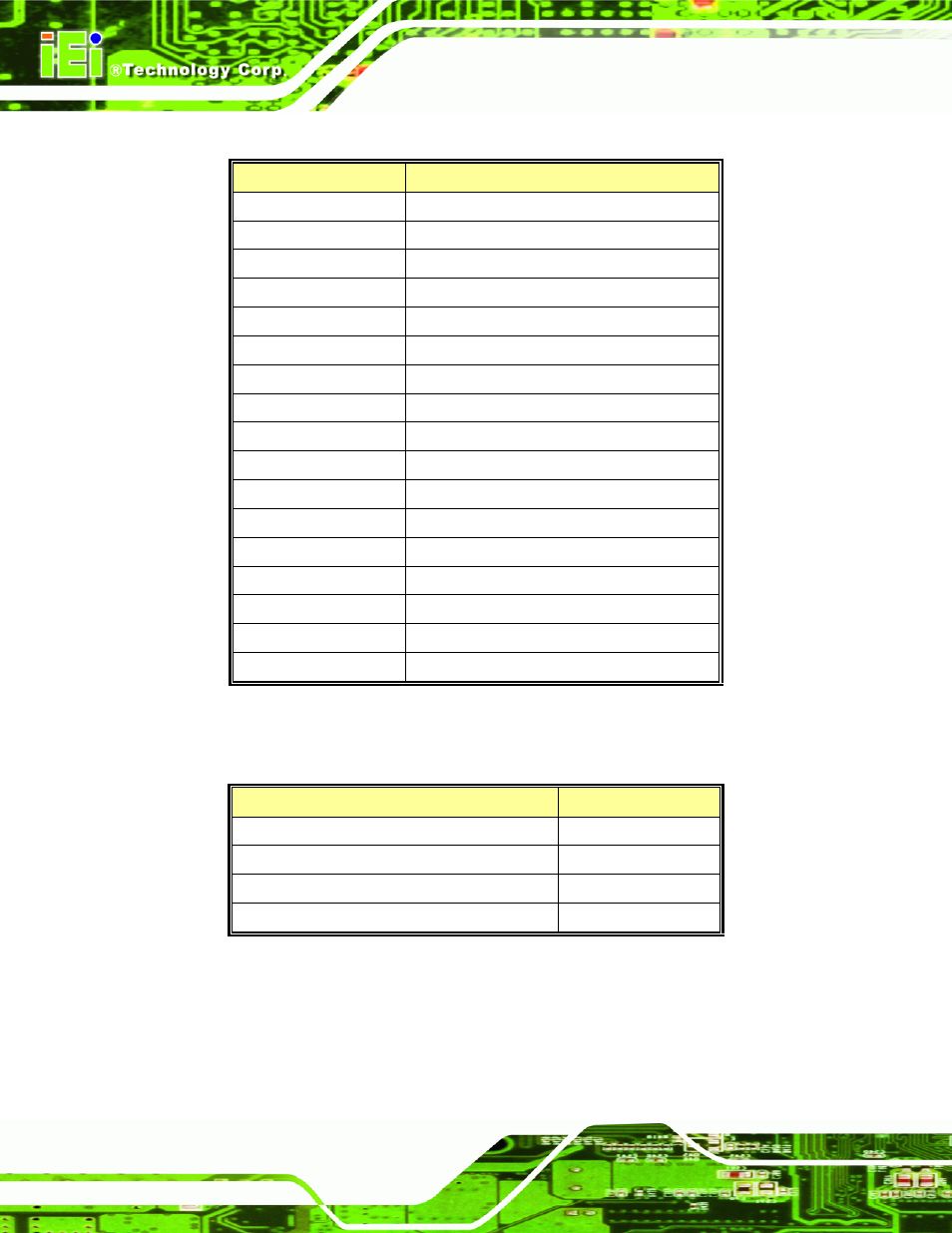

D.1 Address Map

I/O address Range

Description

000-01F DMA

Controller

020-021 Interrupt

Controller

040-043 System

time

060-06F Keyboard

Controller

070-07F

System CMOS/Real time Clock

080-09F DMA

Controller

0A0-0A1 Interrupt

Controller

0C0-0DF DMA

Controller

0F0-0FF

Numeric data processor

1F0-1F7 Primary

IDE

Channel

2F8-2FF

Serial Port 2 (COM2)

378-37F

Parallel Printer Port 1 (LPT1)

3B0-3BB Intel®

Graphics

Controller

3C0-3DF Intel®

Graphics

Controller

3F6-3F6 Primary

IDE

Channel

3F7-3F7

Standard floppy disk controller

3F8-3FF

Serial Port 1 (COM1)

Table D-1: IO Address Map

D.2 1st MB Memory Address Map

Memory address

Description

00000-9FFFF System

memory

A0000-BFFFF VGA

buffer

F0000-FFFFF System

BIOS

1000000-

Extend BIOS

Table D-2: 1

st

MB Memory Address Map

- SPCIE-5100DX (180 pages)

- SPCIE-C2060 v1.01 (200 pages)

- SPCIE-C2060 v2.12 (212 pages)

- SPCIE-C2160 (204 pages)

- SPCIE-C2260-i2 (217 pages)

- ROCKY-3786 v4.0 (175 pages)

- ROCKY-3786 v4.10 (147 pages)

- PCIE-Q350 v1.12 (250 pages)

- PCIE-Q350 v1.20 (250 pages)

- PCIE-Q350 v1.30 (213 pages)

- PCIE-Q57A (159 pages)

- PCIE-G41A2 (151 pages)

- PCIE-Q670 v1.03 (206 pages)

- PCIE-Q670 v2.00 (205 pages)

- PCIE-H610 (181 pages)

- PCIE-Q870-i2 (217 pages)

- IOWA-LX-600 (159 pages)

- PCISA-945GSE v1.01 (207 pages)

- PCISA-945GSE v1.10 (190 pages)

- PCISA-9652 v1.00 (232 pages)

- PCISA-9652 v1.01 (232 pages)

- PCISA-PV-D4251_N4551_D5251 (145 pages)

- PICOe-945GSE (197 pages)

- PICOe-GM45A (198 pages)

- PICOe-PV-D4251_N4551_D5251 v1.00 (154 pages)

- PICOe-PV-D4251_N4551_D5251 v1.10 (154 pages)

- PICOe-PV-D4251_N4551_D5251 v1.11 (155 pages)

- PICOe-B650 (156 pages)

- PICOe-HM650 (174 pages)

- HYPER-KBN (139 pages)

- SPXE-14S (3 pages)

- SPXE-9S v1.00 (5 pages)

- SPXE-9S v1.1 (6 pages)

- SPE-9S v1.00 (4 pages)

- SPE-9S v1.1 (5 pages)

- SPE-6S (3 pages)

- SPE-4S (4 pages)

- PE-6SD3 (4 pages)

- PE-6SD2 v4.0 (4 pages)

- PE-6SD2 v2.10 (3 pages)

- PE-6SD (3 pages)

- PE-6S3 v1.0 (2 pages)

- PE-6S3 v4.0 (4 pages)

- PE-6S2 (4 pages)