Teledyne LeCroy SDA II User Manual

Page 17

Operator's Manual

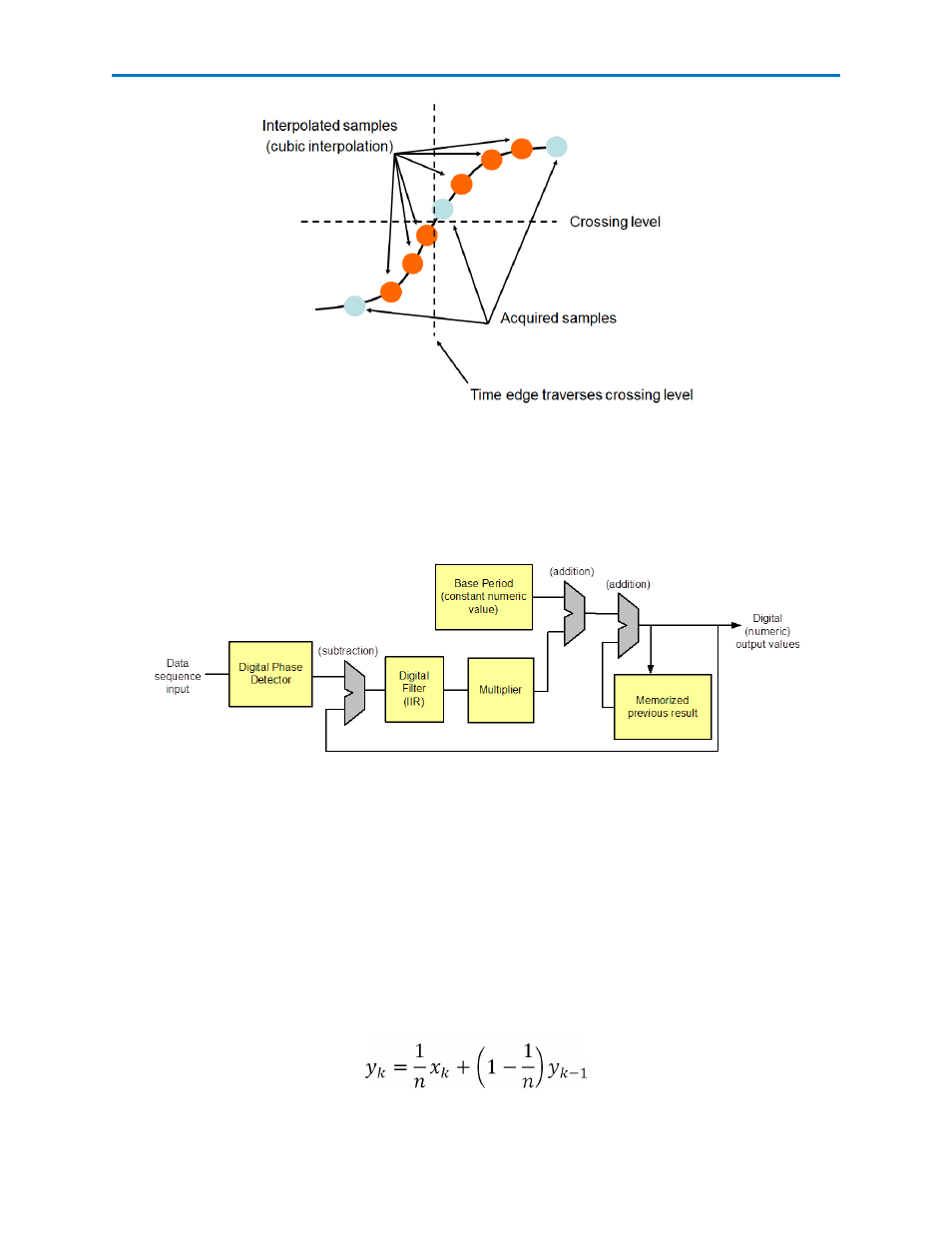

SDA Edge Time Determination

Clock recovery implementation in the SDA is shown in the following figure. This algorithm generates time

values corresponding to a clock at the data rate. The computation follows variations in the data stream

being tested through the use of a feedback control loop correcting each period of the clock by adding a

portion of the error between the recovered clock edge and the nearest data edge.

Clock Recovery Implementation Using a PLL

As shown in the previous image, the initial output and the output of the digital phase detector are set to

zero. The next time value output is equal to the nominal data rate. This value is fed back to the com-

parator on the far left which compares this time value to the measured time of the next data edge from

the digital phase detector. The difference is the error between the data rate and the recovered clock, and

can also incorporate the measurement of the number of UI's since the last edge (that is, the local tran-

sition density).This difference is filtered and added to the initial base period to then generate the cor-

rected clock period. The filter controls the rate of this correction by scaling the amount of error fed back

to the clock period computation. The choice of filter in SDAII and SDAIII-CompleteLinQ includes a single-

pole infinite impulse response (IIR) low-pass filter (the golden PLL, as defined by FibreChannel), a 1 pole 1

zero filter, and a 2 pole 1 zero filter. The equation of the golden PLL 1 pole filter is:

922968 Rev A

15