Pll setup – Teledyne LeCroy SDA II User Manual

Page 14

Serial Data Analysis II Software

This section duplicates controls found elsewhere: the Use Explicit Clock Ref checkbox (serving the same

function as the multiplexer switch on the SDAII dialog) and the Multiplier field (also found on the Ref

Clock dialog).

PLL Setup

The PLL Setup section of the Clock Recoverydialog contains the controls to set the type and bandwidth

of the digital PLL used in all SDAII measurements. The PLL bandwidth limits the response of the recovered

clock to high rate variations in the data rate. Configure this section to match the behavior of your receiv-

er's PLL.

Example: A PLL bandwidth of 5 MHz allows the recovered clock to track frequency variations below

approximately half the frequency, therefore removing the effect from jitter and eye pattern meas-

urements. The software PLL implemented in SDAII allows you to choose among several types of PLL.

The selected PLL is applied to either the data stream under test or the selected clock source (if a Ref-

erence Clock is in use) when the PLL On control is checked. The PLL recovers a reference clock from the

selected source, which is used by all subsequent SDAII measurements.

PLL Types

FC G

OLDEN

FC Golden is the default selection and implements the golden PLL as defined in the Fibrechannel spec-

ification. By default, the golden PLL is set to a cutoff frequency of 1/1667 times the bit rate of the signal

under test. This ratio can be adjusted from 1/10 to 1/1e6.

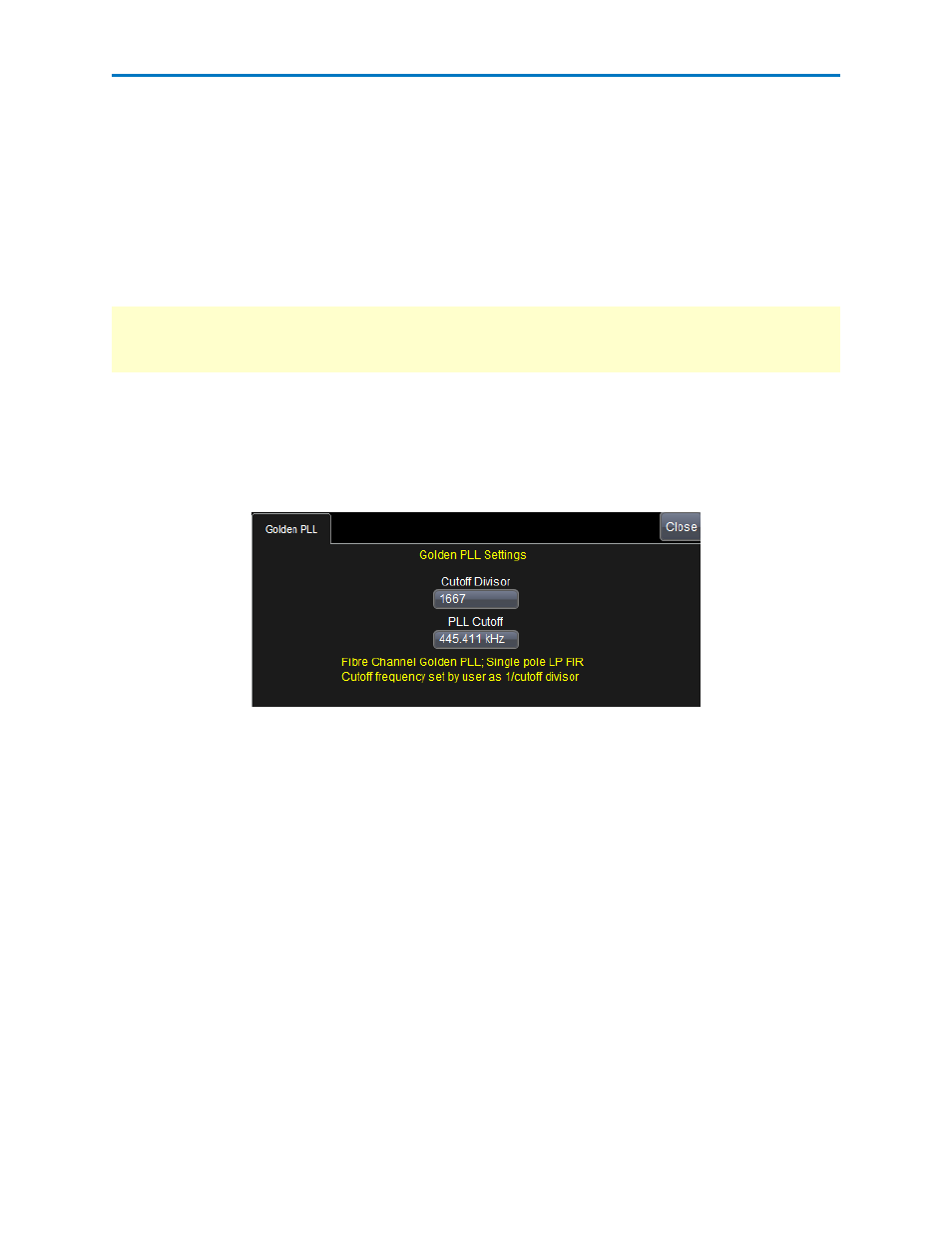

Make the following settings for the FC Golden PLL on the Golden PLL dialog at the far right of the screen:

l

Touch inside the Cutoff Divisorfield and enter a value using the pop-up keypad. The default value

of 1667 is the industry standard for a Golden PLL and equals the ratio of the Bit Rate to the PLL Cut-

off frequency.

The PLL cutoff divisor is the value by which the bit rate is divided to compute the cutoff frequency

for the loop bandwidth of the clock recovery operation for sequential eye pattern, jitter, and bit

error rate functions. This control is variable from 10 to 1,000. A low PLL cutoff divisor means the

PLL tracks and, therefore, attenuates jitter at higher frequencies.The default value of 1667 causes

the clock recovery to operate as a golden PLL, as defined in the Fibrechannel specification.

l

The PLL Cutoff frequency control reads the frequency corresponding to the Cutoff Divisor. Alter-

natively, the PLL Cutoff frequency may be provided and the nearest cutoff divisor is then com-

puted from the entry.

12

922968 Rev A