Impulse 7204 User Manual

Page 14

Technical

Description

Sealevel Systems ULTRA 485+2.PCI Page

11

Why use an ISP?

The answer to the polling inefficiency was the Interrupt Status Port (ISP). The

ISP is a read only 8-bit register that sets a corresponding bit when an interrupt is

pending. Port 1 interrupt line corresponds with Bit D0 of the status port, Port 2

with D1 etc. The use of this port means that the software designer now only has

to poll a single port to determine if an interrupt is pending.

The ISP is at Base+7 on each port (Example: Base = 280 Hex, Status Port = 287,

28F… etc.). The ULTRA 485+2.PCI will allow any one of the available

locations to be read to obtain the value in the status register. Both status ports on

the ULTRA 485+2.PCI are identical, so any one can be read.

Example: This indicates that Channel 2 has an interrupt pending.

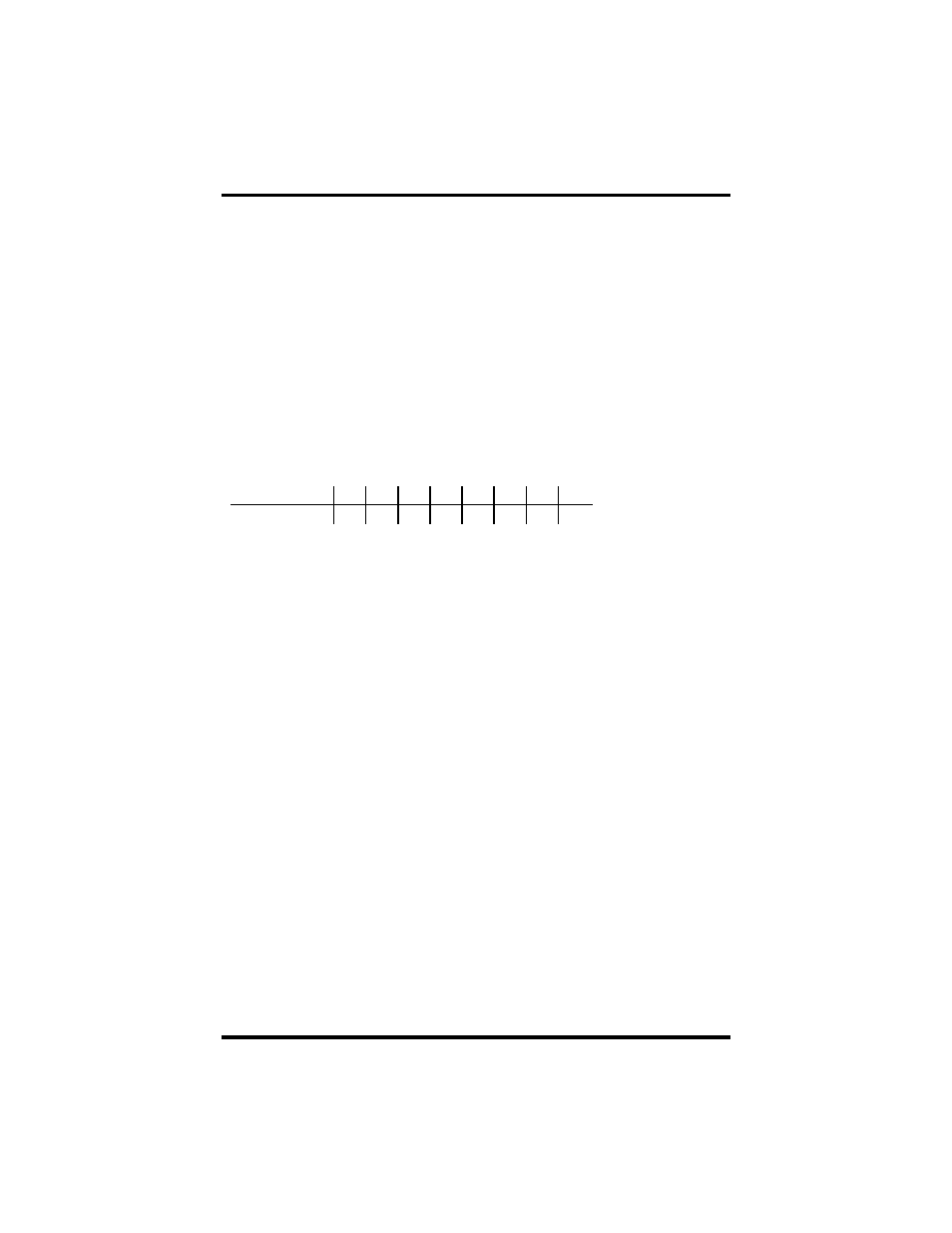

Bit

Position: 7 6 5 4 3 2 1 0

Value

Read: 0 0 0 0 0 0 1

0

- PCW-5181 (120 pages)

- PCM-4373 (2 pages)

- EPIC-5536 (2 pages)

- EPIC-CV07 (2 pages)

- EPIC-QM57 (2 pages)

- EPIC-QM77 (2 pages)

- VSX-6118-V2 (1 page)

- VSX-6116-V2 (1 page)

- VSX-6115-V2 (1 page)

- VSX-6114-V2 (1 page)

- VDX-6318RD (1 page)

- VDX-6316RD (1 page)

- VDX-6315RD (1 page)

- VDX-6314RD (1 page)

- PCM-5895 Rev. A (2 pages)

- PCM-8120 (2 pages)

- PCM-9562 (3 pages)

- VSX-6127-V2 (1 page)

- PCM-9375 (3 pages)

- GENE-5315W1 Rev. B (2 pages)

- GENE-5315 Rev. A (2 pages)

- VDX-6327RD (1 page)

- VDX-6328RD (1 page)

- VDX-6329RD (1 page)

- VDX-6326RD (1 page)

- PCM-9343 (3 pages)

- GENE-9655 (2 pages)

- PCM-9362 (2 pages)

- GENE-LN05W2 Rev. B (2 pages)

- PCM-9363 (3 pages)

- GENE-TC05W2 (2 pages)

- GENE-CV05W2 (2 pages)

- SBC-210 (1 page)

- GENE-QM57 (2 pages)

- GENE-QM67 (2 pages)

- GENE-QM77 Rev B (2 pages)

- GENE-QM77 Rev A (2 pages)

- GENE-QM87 (1 page)

- EL630-NR (2 pages)

- EL620-C (2 pages)

- SB601-C (2 pages)

- SB600-C (2 pages)

- SB630-CRM (2 pages)

- CL630-CRM (2 pages)

- DL631-C226 (2 pages)