A.1 watchdog timer registers – AAEON TKS-P20-CV01 User Manual

Page 76

E m b e d d e d B o x

T K S - G 2 1 - C V 0 5

Appendix A Programming the Watchdog Timer A-2

A.1 Watchdog Timer Registers

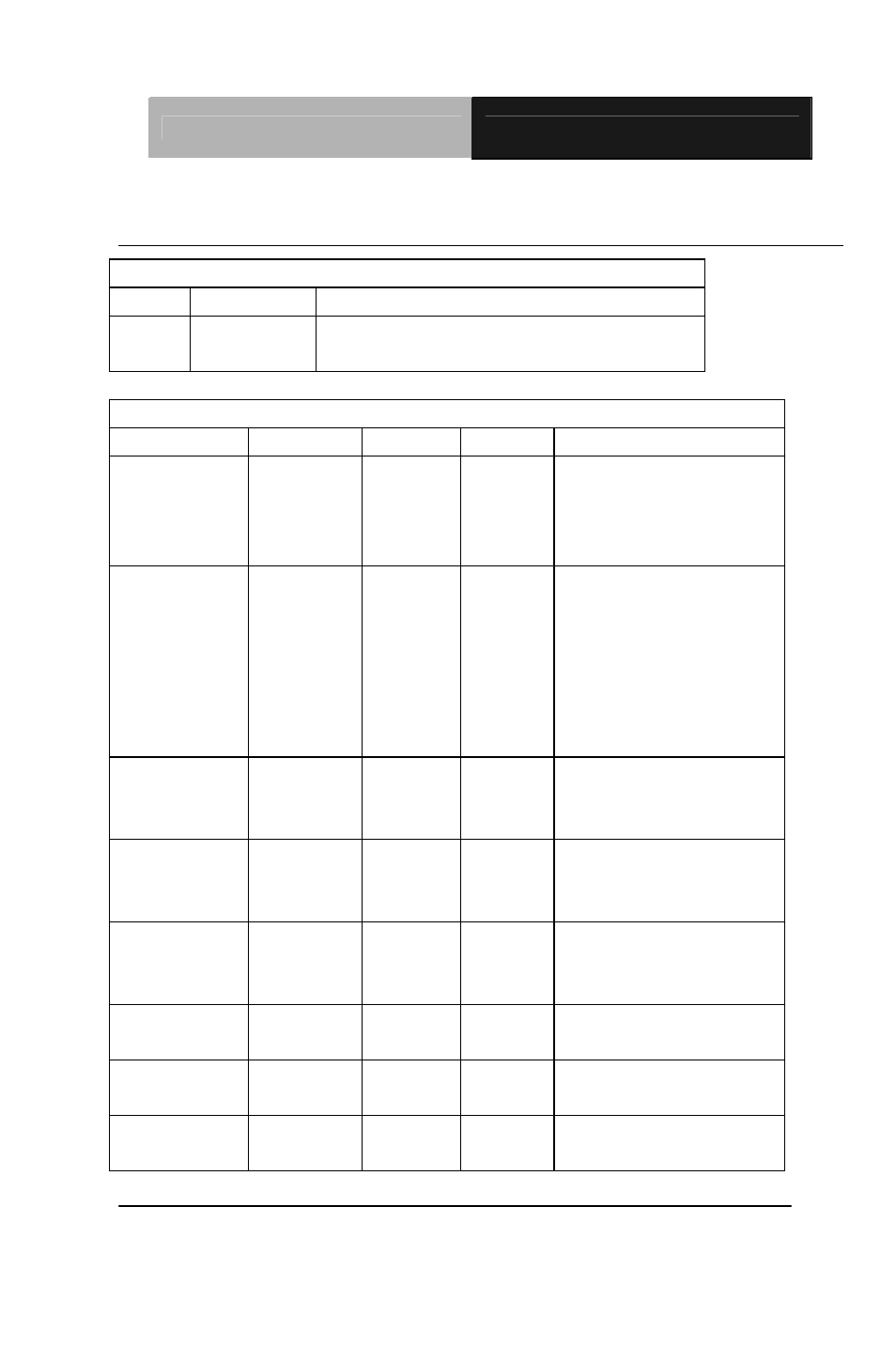

Table 1 : Watch dog relative IO address

Default Value

Note

I/O Base

Address

0xA00

I/O Base address for Watchdog operation.

This address is assigned by SIO LDN7, register 0x60‐0x61.

Table 2 : Watchdog relative register table

Register

Offset

BitNum

Value

Note

Watchdog

WDTRST# Enable

0x00

7

1

Enable/Disable

time out output via WDTRST#

0: Disable

1: Enable

Pulse Width

0x05

0:1

01

Width of Pulse signal

00: 1ms (do not use)

01: 25ms

10: 125ms

11: 5s

Pulse width is must longer then

16ms.

Signal Polarity

0x05

2

0

0: low active

1: high active

Must set this bit to 0

Counting Unit

0x05

3

0

Select time unit.

0: second

1: minute

Output Signal

Type

0x05

4

1

0: Level

1: Pulse

Must set this bit to 1

Watchdog Timer

Enable

0x05

5

1

0: Disable

1: Enable

Timeout Status

0x05

6

1

1: timeout occurred. Write a 1

to clear timeout status

Timer Counter

0x06

Time of watchdog timer

(0~255)