Ap7168, 2a low dropout regulator with pok, New prod uc t electrical characteristics – Diodes AP7168 User Manual

Page 3: Vδv δv

AP7168

1.2A LOW DROPOUT REGULATOR WITH POK

AP7168

Document number: DS32019 Rev. 2 - 2

3 of 11

September 2010

© Diodes Incorporated

NEW PROD

UC

T

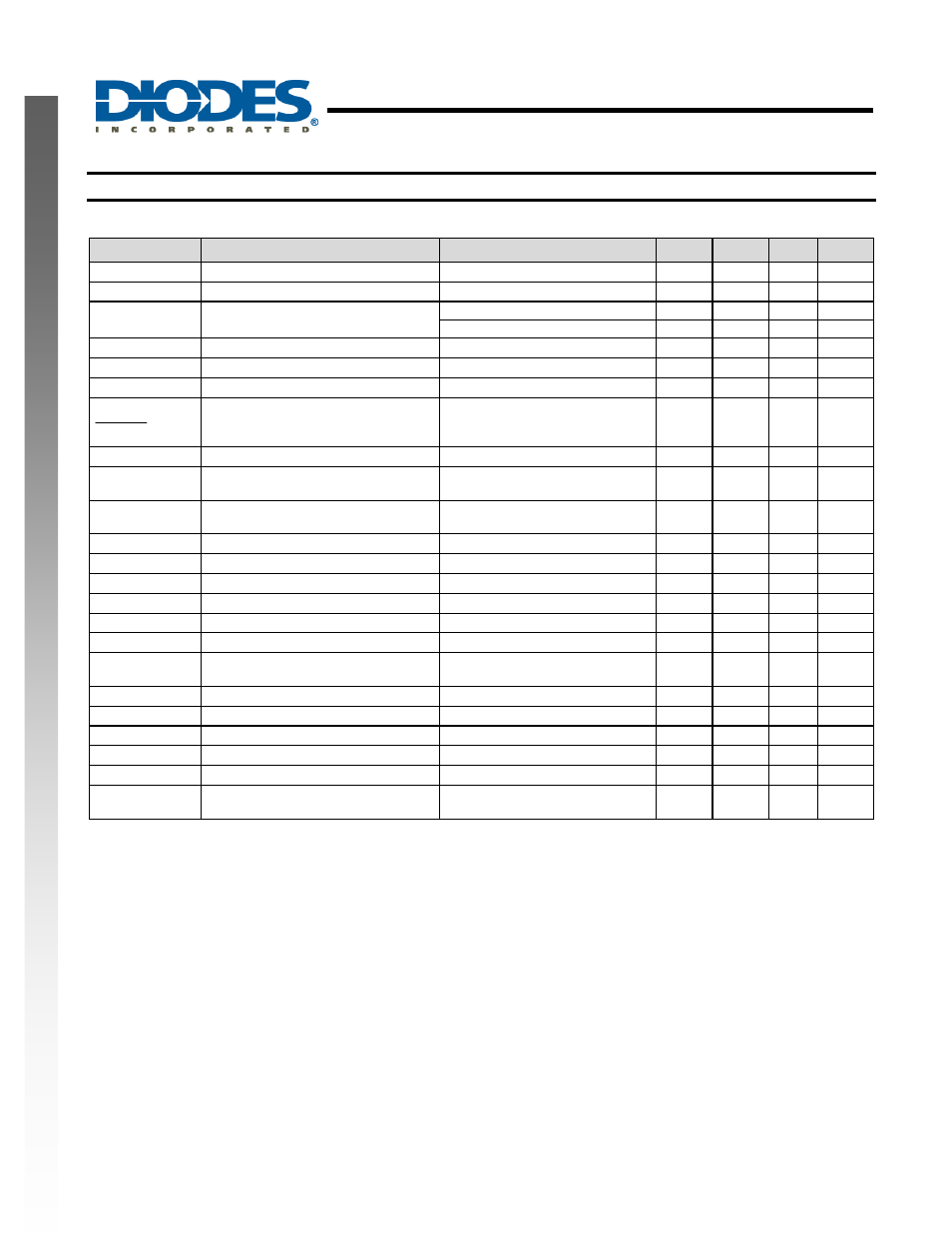

Electrical Characteristics

(T

A

= 25

o

C, V

IN

= V

OUT

+1V, C

IN

= 1

μF, C

OUT

= 1

μF, V

EN

= 2V, unless otherwise stated)

Symbol

Parameter

Test Conditions

Min

Typ.

Max

Unit

I

Q

Input Quiescent Current

I

OUT

= 0

⎯

125 180 µA

I

SHDN

Input Shutdown Current

V

EN

= 0V, I

OUT

= 0 (Note 3)

-1

0.1

1

µA

V

Dropout

Dropout Voltage

V

OUT

≥ 1.5V, I

OUT

= 0.5A

230 mV

V

OUT

≥ 1.5V, I

OUT

= 1A

500

800

mV

V

REF

FB reference voltage

0.8

V

I

FB

FB leakage

⎯

0.01 1 µA

V

OUT

Output Voltage Total Accuracy

-3

3

%

OUT

IN

OUT

V

ΔV

ΔV

/

Line Regulation

V

IN

= V

OUT

+1V to 5.5V,

I

OUT

= 1mA

0.02 %/V

ΔV

OUT

/ V

OUT

Load Regulation

I

OUT

from 1mA to 1A

-1.5

1.5

%

t

ST

Start-up Time, from EN high to POK

high

V

EN

= 0V to 2.0V, I

OUT

= 100mA,

V

IN

= 3.3V

190 µs

PSRR

Power Supply Rejection Ratio

1kHz, V

IN

= 3.3V, V

OUT

= 1.2V,

I

OUT

= 100mA

60 dB

I

LIMIT

Current limit

V

OUT

= 1.8V, R

OUT

= 0.5

Ω

1.2 1.6 A

I

SHORT

Short-circuit Current

V

IN

= 3.3V, V

OUT

< 0.2V

750

mA

V

IL

EN Input Logic Low Voltage

0.4

V

V

IH

EN Input Logic High Voltage

1.4

V

I

EN

EN Input leakage

V

EN

= 0V or 5.5V

⎯

0.01 1 µA

V

OL

POK output low voltage

Force 2mA

100

200

mV

V

POK_TH_UP

Output voltage (rising) POK threshold

FB (or OUT for fixed version)

rising

87% 92% 97% V

ref

V

POK_Hys

Output voltage POK hysteresis

4%

V

ref

POK deglitch

V

IN

= 3.3V, V

OUT

= 1.2V

160

µs

I

POK_LK

POK leakage current

V

POK

= 5.5V

⎯

0.01 1 µA

T

SHDN

Thermal shutdown threshold

145

°C

T

HYS

Thermal shutdown hysteresis

25

°C

θ

JA

Thermal Resistance Junction-to-

Ambient

SOP-8L-EP (Note 4)

27

o

C/W

Notes:

3. POK pin must be disconnected from IN pin.

4

. Test condition for SO-8EP:

Device mounted on 2" x 2" FR-4 substrate PCB, 2oz copper, with minimum recommended pad on top

layer and thermal vias to bottom layer ground plane.