0 functional description – Rainbow Electronics LM82 User Manual

Page 11

1.0 Functional Description

(Continued)

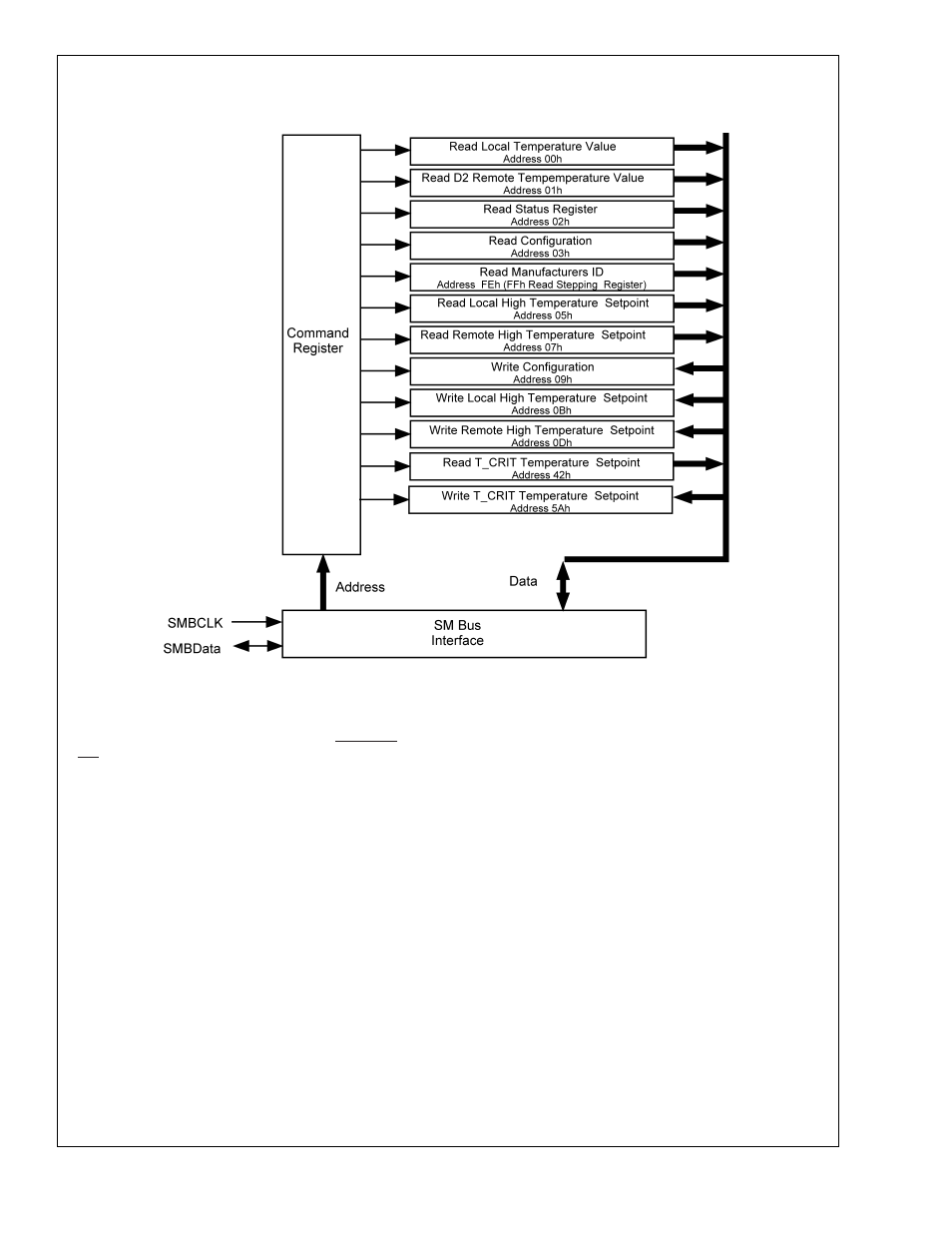

1.9 COMMUNICATING with the LM82

There are 13 data registers in the LM82, selected by the

Command Register. At power-up the Command Register is

set to “00”, the location for the Read Local Temperature Reg-

ister. The Command Register latches the last location it was

set to. Reading the Status Register resets T_CRIT_A and

INT, so long as a temperature comparison does not signal a

fault (see

Sections 1.2 and 1.3). All other registers are pre-

defined as read only or write only. Read and write registers

with the same function contain mirrored data.

A Write to the LM82 will always include the address byte and

the command byte. A write to any register requires one data

byte.

Reading the LM82 can take place either of two ways:

1.

If the location latched in the Command Register is cor-

rect (most of the time it is expected that the Command

Register will point to one of the Read Temperature Reg-

isters because that will be the data most frequently read

from the LM82), then the read can simply consist of an

address byte, followed by retrieving the data byte.

2.

If the Command Register needs to be set, then an ad-

dress byte, command byte, repeat start, and another ad-

dress byte will accomplish a read.

The data byte has the most significant bit first. At the end of

a read, the LM82 can accept either Acknowledge or No Ac-

knowledge from the Master (No Acknowledge is typically

used as a signal for the slave that the Master has read its

last byte).

1.10 SERIAL INTERFACE ERROR RECOVERY

The LM82 SMBus lines will be reset to the SMBus idle state

if the SMBData or SMBCLK lines are held low for 40 ms or

more (t

TIMEOUT

). The LM82 may or may not reset the state of

the serial interface logic if either of the SMBData or SMBCLK

lines are held low between 25 ms and 40 ms. TIMEOUT al-

lows a clean recovery in cases where the master may be re-

set while the LM82 is transmitting a low bit thus preventing

possible bus lock up.

Whenever the LM82 sees the start condition its serial inter-

face will reset to the beginning of the communication, thus

the LM82 will expect to see an address byte next. This sim-

plifies recovery when the master is reset while the LM82 is

transmitting a high.

DS101297-9

LM82

www.national.com

11