Detailed description – Rainbow Electronics DS1086L User Manual

Page 8

DS1086

DS1086 Spread-Spectrum EconOscillator

8

_____________________________________________________________________

Detailed Description

A block diagram of the DS1086 is shown in Figure 3.

The internal master oscillator generates a square wave

with a 66MHz to 133MHz frequency range. The fre-

quency of the master oscillator can be programmed

with the DAC register over a two-to-one range in 10kHz

steps. The master oscillator range is larger than the

range possible with the DAC step size, so the OFFSET

register is used to select a smaller range of frequencies

over which the DAC spans. The prescaler can then be

set to divide the master oscillator frequency by 2

x

(where x equals 0 to 8) before routing the signal to the

output (OUT) pin.

A programmable triangle-wave generator injects an off-

set element into the master oscillator to dither its output

2% or 4%. The dither is controlled by the J0 bit in the

PRESCALER register and enabled with the SPRD pin.

The maximum spectral attenuation occurs when the

prescaler is set to 1. The spectral attenuation is

reduced by 2.7dB for every factor of 2 that is used in

the prescaler. This happens because the prescaler’s

divider function tends to average the dither in creating

the lower frequency. However, the most stringent spec-

tral emission limits are imposed on the higher frequen-

cies where the prescaler is set to a low divider ratio.

The external control input, OE, gates the clock output

buffer. The

PDN pin disables the master oscillator and

turns off the clock output for power-sensitive applica-

tions*. On power-up, the clock output is disabled until

power is stable and the master oscillator has generated

512 clock cycles. Both controls feature a synchronous

enable that ensures there are no output glitches when

the output is enabled, and a constant time interval (for a

given frequency setting) from an enable signal to the

first output transition.

The control registers are programmed through a 2-wire

interface and are used to determine the output frequen-

cy and settings. Once programmed into EEPROM,

since the register settings are NV, the settings only

need to be reprogrammed if it is desired to reconfigure

the device.

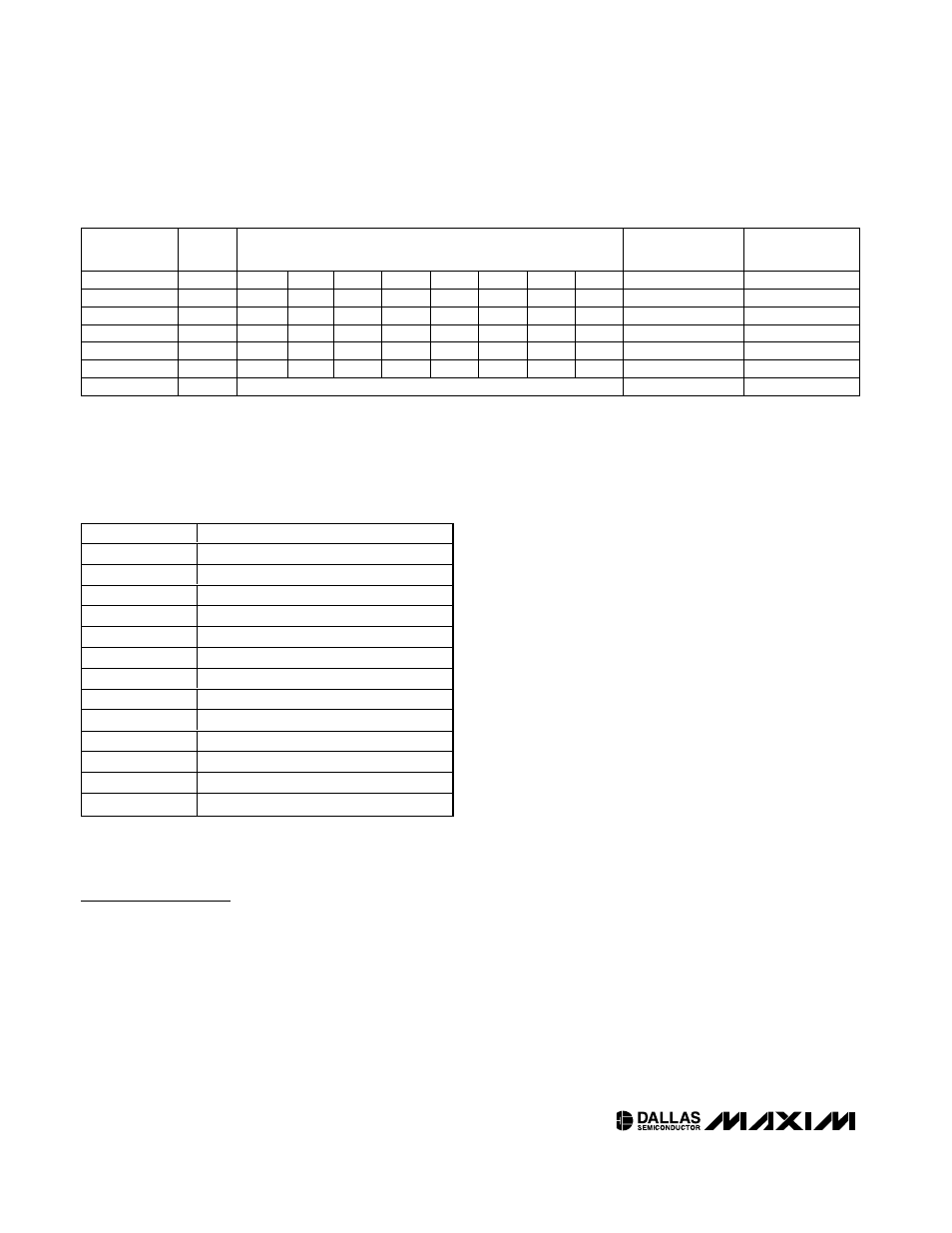

OFFSET

FREQUENCY RANGE (MHz)

OS - 6

61.44 to 71.67

OS - 5

66.56 to 76.79

OS - 4

71.68 to 81.91

OS - 3

76.80 to 87.03

OS - 2

81.92 to 92.15

OS - 1

87.04 to 97.27

OS*

92.16 to 102.39

OS + 1

97.28 to 107.51

OS + 2

102.40 to 112.63

OS + 3

107.52 to 117.75

OS + 4

112.64 to 122.87

OS + 5

117.76 to 127.99

OS + 6

122.88 to 133.11

*Factory default setting. OS is the integer value of the 5 LSBs

of the RANGE register.

REGISTER

ADDR

MSB

BINARY

LSB

FACTORY

DEFAULT

ACCESS

PRESCALER

02h

X

1

X

1

X

X

J0

P3

P2

P1

P0

11100000b

R/W

DAC HIGH

08h

b9

b8

b7

b6

b5

b4

b3

b2

01111101b

R/W

DAC LOW

09h

b1

b0

X

0

X

0

X

0

X

0

X

0

X

0

00000000b

R/W

OFFSET

0Eh

X

1

X

1

X

1

b4

b3

b2

b1

b0

1 1 1 - - - - - b

R/W

ADDR

0Dh

X

1

X

1

X

1

X

1

WC

A2

A1

A0

11110000b

R/W

RANGE

37h

X

X

X

X

X

X

b4

b3

b2

b1

b0

x x x - - - - - b

R

WRITE EE

3Fh

NO DATA

—

—

Table

1. Register Summary

X

0

= Don’t care, reads as zero.

X

1

= Don’t care, reads as one.

X

X

= Don’t care, reads indeterminate.

X = Don’t care.

Table

2. Offset Settings

*The power-down command must persist for at least two out-

put frequency cycles plus 10µs for deglitching purposes.