Table 1. time-of-day alarm mask bits, Special purpose registers, Control register (read 0fh, write 8fh) – Rainbow Electronics DS1306 User Manual

Page 7: Status register (read 10h)

DS1306

7 of 21

During each clock update, the RTC compares the Alarm 0 and Alarm 1 registers with the corresponding

clock registers. When a match occurs, the corresponding alarm flag bit in the status register is set to a 1. If

the corresponding alarm interrupt enable bit is enabled, an interrupt output is activated.

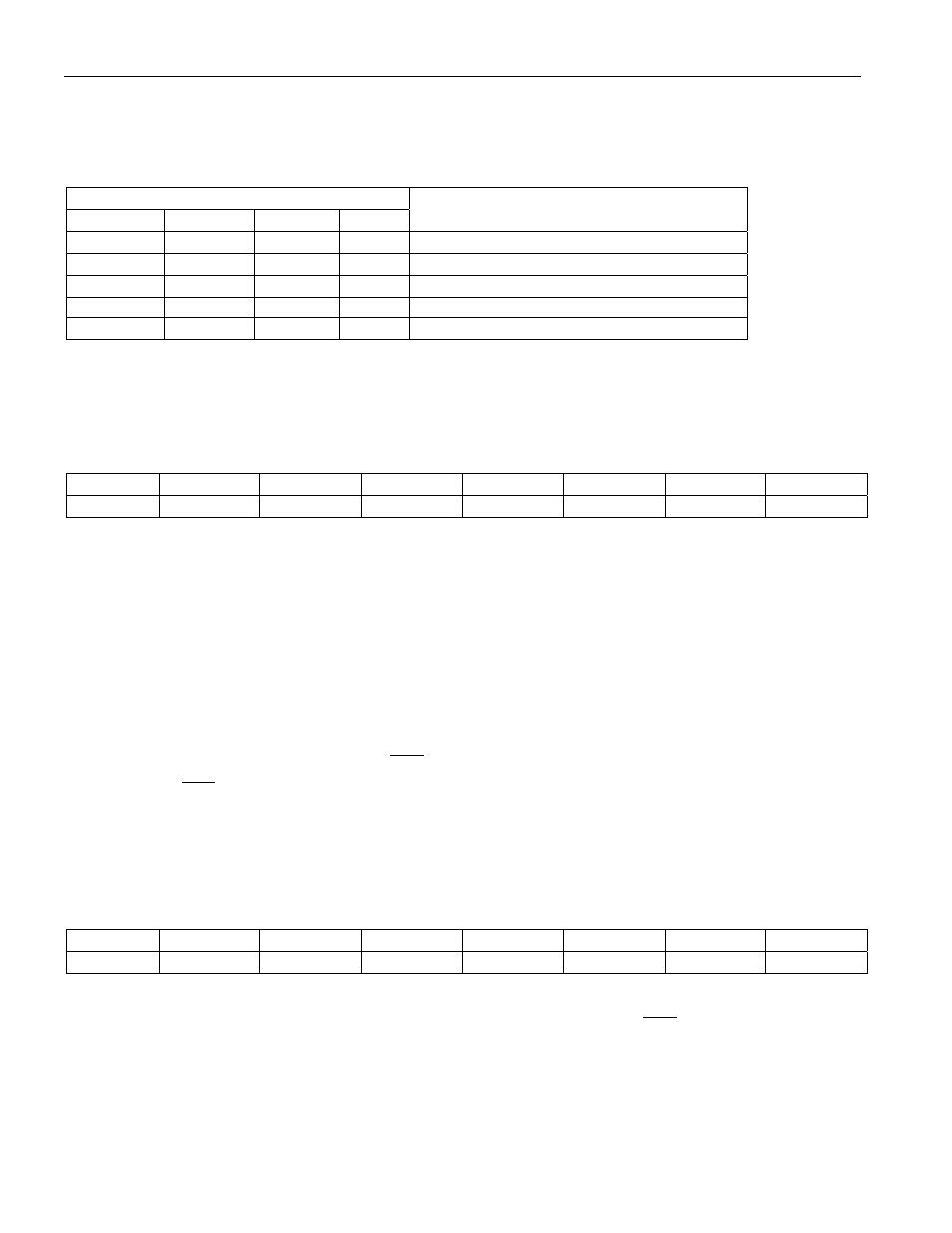

Table 1. TIME-OF-DAY ALARM MASK BITS

ALARM REGISTER MASK BITS (BIT 7)

SECONDS

MINUTES

HOURS

DAYS

FUNCTION

1

1

1

1

Alarm once per second

0

1

1

1

Alarm when seconds match

0

0

1

1

Alarm when minutes and seconds match

0

0

0

1

Alarm hours, minutes, and seconds match

0

0

0

0

Alarm day, hours, minutes and seconds match

SPECIAL PURPOSE REGISTERS

The DS1306 has three additional registers (control register, status register, and trickle charger register)

that control the real-time clock, interrupts, and trickle charger.

CONTROL REGISTER (READ 0FH, WRITE 8FH)

BIT7

BIT6

BIT5

BIT4

BIT3

BIT2

BIT1

BIT0

0

WP

0

0

0

1 Hz

AIE1

AIE0

WP (Write Protect) – Before any write operation to the clock or RAM, this bit must be logic 0. When

high, the write protect bit prevents a write operation to any register, including bits 0, 1, and 2 of the

control register. Upon initial power-up, the state of the WP bit is undefined. Therefore, the WP bit should

be cleared before attempting to write to the device. When WP is set, it must be cleared before any other

control register bit can be written.

1Hz (1Hz Output Enable) – This bit controls the 1Hz output. When this bit is a logic 1, the 1Hz output

is enabled. When this bit is a logic 0, the 1Hz output is high-Z.

AIE0 (Alarm Interrupt Enable 0) – When set to a logic 1, this bit permits the interrupt 0 request flag

(IRQF0) bit in the status register to assert

INT0

. When the AIE0 bit is set to logic 0, the IRQF0 bit does

not initiate the

INT0

signal.

AIE1 (Alarm Interrupt Enable 1) – When set to a logic 1, this bit permits the interrupt 1 request flag

(IRQF1) bit in the status register to assert INT1. When the AIE1 bit is set to logic 0, the IRQF1 bit does

not initiate an interrupt signal, and the INT1 pin is set to a logic 0 state.

STATUS REGISTER (READ 10H)

BIT7

BIT6

BIT5

BIT4

BIT3

BIT2

BIT1

BIT0

0

0

0

0

0

0

IRQF1

IRQF0

IRQF0 (Interrupt 0 Request Flag) – A logic 1 in the interrupt request flag bit indicates that the current

time has matched the Alarm 0 registers. If the AIE0 bit is also a logic 1, the

INT0

pin goes low. IRQF0 is

cleared when the address pointer goes to any of the Alarm 0 registers during a read or write. IRQF0 is

activated when the device is powered by V

CC1

, V

CC2

, or V

BAT

.

IRQF1 (Interrupt 1 Request Flag) – A logic 1 in the interrupt request flag bit indicates that the current

time has matched the Alarm 1 registers. If the AIE1 bit is also a logic 1, the INT1 pin generates a 62.5ms