Ac electrical characteristics – Rainbow Electronics DS1337 User Manual

Page 3

DS1337 I

2

C Serial Real-Time Clock

3 of 15

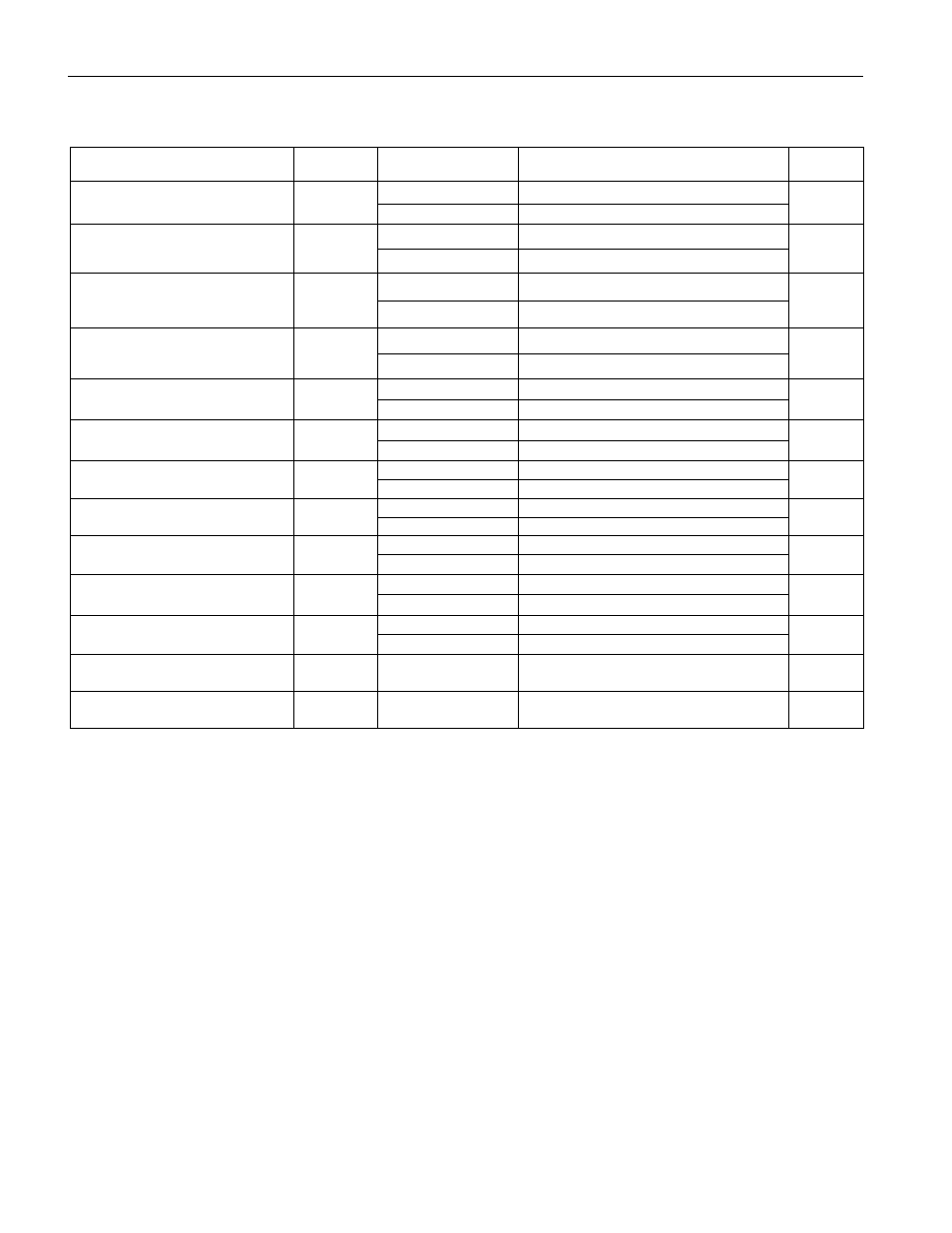

AC ELECTRICAL CHARACTERISTICS

(V

CC

= 1.8V to 5.5V, T

A

= -40°C to +85°C.) (Note 1)

PARAMETER SYMBOL

CONDITIONS

MIN TYP

MAX

UNITS

Fast mode

100

400

SCL Clock Frequency

f

SCL

Standard mode

100

kHz

Fast mode

1.3

Bus Free Time Between a

STOP and START Condition

t

BUF

Standard mode

4.7

ms

Fast mode

0.6

Hold Time (Repeated)

START Condition (Note 10)

t

HD:STA

Standard mode

4.0

ms

Fast mode

1.3

LOW Period of SCL Clock

t

LOW

Standard mode

4.7

ms

Fast mode

0.6

HIGH Period of SCL Clock

t

HIGH

Standard mode

4.0

ms

Fast mode

0.6

Setup Time for a Repeated

START Condition

t

SU:STA

Standard mode

4.7

ms

Fast mode

0

0.9

Data Hold Time

(Notes 11, 12)

t

HD:DAT

Standard mode

0

ms

Fast mode

100

Data Setup Time (Note 13)

t

SU:DAT

Standard mode

250

ns

Fast mode

20 + 0.1C

B

300

Rise Time of Both SDA and

SCL Signals (Note 14)

t

R

Standard mode

20 + 0.1C

B

1000

ns

Fast mode

20 + 0.1C

B

300

Fall Time of Both SDA and

SCL Signals (Note 14)

t

F

Standard mode

20 + 0.1C

B

300

ns

Fast mode

0.6

Setup Time for STOP

Condition

t

SU:STO

Standard mode

4.0

ms

Capacitive Load for Each Bus

Line

C

B

(Note

14)

400 pF

I/O Capacitance (SDA, SCL)

C

I/O

(Note

15)

10

pF

Note 1:

Limits at -40°C are guaranteed by design and are not production tested.

Note 2:

SCL only.

Note 3:

SDA,

INTA, and SQW/INTB.

Note 4:

I

CCA

—SCL clocking at max frequency = 400kHz, V

IL

= 0.0V, V

IH

= V

CC.

Note 5:

Specified with the I

2

C bus inactive, V

IL

= 0.0V, V

IH

= V

CC.

Note 6:

SQW enabled.

Note 7:

Specified with the SQW function disabled by setting INTCN = 1.

Note 8:

Using recommended crystal on X1 and X2.

Note 9:

The device is fully accessible when 1.8

£ V

CC

£ 5.5V. Time and date are maintained when 1.3V £ V

CC

£ 1.8V.

Note 10:

After this period, the first clock pulse is generated

Note 11:

A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the V

IHMIN

of the SCL signal) to

bridge the undefined region of the falling edge of SCL.

Note 12:

The maximum t

HD:DAT

need only be met if the device does not stretch the LOW period (t

LOW

) of the SCL signal.

Note 13:

A fast-mode device can be used in a standard-mode system, but the requirement t

SU:DAT

³ to 250ns must then be met. This is

automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW

period of the SCL signal, it must output the next data bit to the SDA line t

R max

+

t

SU:DAT

= 1000 + 250 = 1250ns before the SCL

line is released.

Note 14:

C

B

—total capacitance of one bus line in pF.

Note 15:

Guaranteed by design. Not production tested.