Rainbow Electronics HT49R70A-1 User Manual

Page 23

HT49R70A-1

Rev. 1.00

23

December 4, 2001

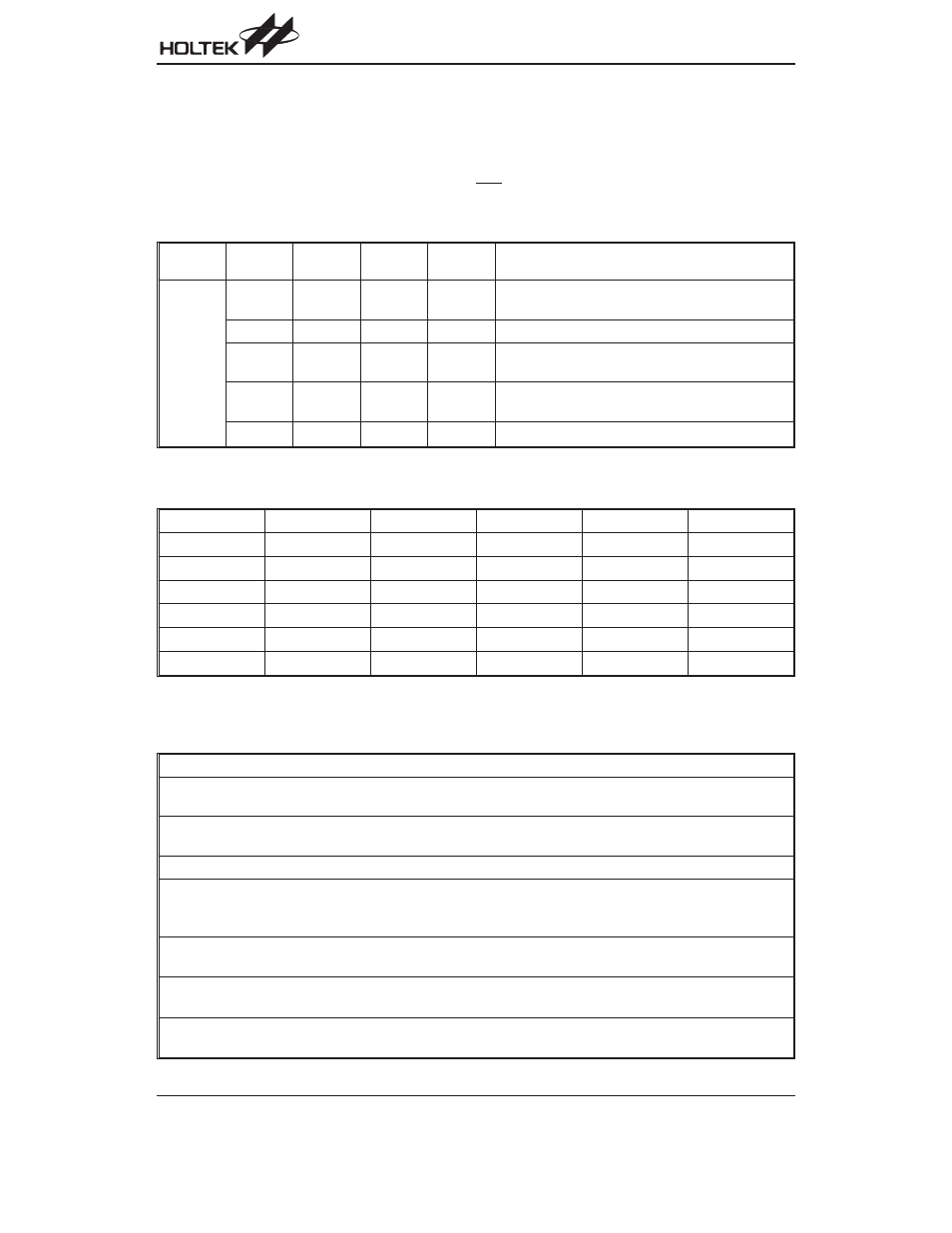

Low voltage reset/detector functions

There is a low voltage detector (LVD) and a low voltage reset circuit (LVR) implemented in the MCU. These two func-

tions can be enabled/disabled by ROM code options. Once the LVD ROM code options is enabled, the user can use the

RTCC.3 to enable/disable (1/0) the LVD circuit and read the LVD detector status (0/1) from RTCC.5; otherwise, the LVD

function is disabled.

The LVR has the same effect or function with the external RES signal which performs chip reset. During HALT state,

LVR is disabled.

The RTCC register definitions are listed in the table on the next page.

Register

Bit No.

Label

Read/

Write

Reset

Function

RTCC

(09H)

0~2

RT0~RT2

R/W

0

8 to 1 multiplexer control inputs to select the real clock

prescaler output

3

LVDC*

R/W

0

LVD enable/disable (1/0)

4

QOSC

R/W

0

32768Hz OSC quick start-up oscillating

0/1: quickly/slowly start

5

LVDO

R/W

0

LVD detection output (1/0)

1: low voltage detected

6~7

¾

¾

¾

Unused bit, read as

²0²

Note:

²*² Once the LVD function is enabled the reference generator should be enabled; otherwise the reference gen-

erator is controlled by LVR ROM code option. The relationship between LVR and LVD options and LVDC are as

shown.

LVD

LVR

LVDC

V

REF

Generator

LVR Comparator LVD Comparator

EN

EN

ON

EN

EN

EN

EN

EN

OFF

EN

EN

DIS

EN

DIS

ON

EN

DIS

EN

EN

DIS

OFF

DIS

DIS

DIS

DIS

EN

X

EN

EN

DIS

DIS

DIS

X

DIS

DIS

DIS

Options

The following shows the mask options in the HT49R70A-1. All these options should be defined in order to ensure

proper functioning system.

Options

OSC type selection. This option is to decide if an RC or crystal or 32768Hz crystal oscillator is chosen as system

clock.

WDT Clock source selection. RTC and Time Base. There are three types of selections: system clock/4 or RTC OSC

or WDT OSC.

WDT enable/disable selection. WDT can be enabled or disabled by option.

CLR WDT times selection. This option defines the method to clear the WDT by instruction.

²One time² means that

the

²CLR WDT² can clear the WDT. ²Two times² means only if both of the ²CLR WDT1² and ²CLR WDT2² have been

executed, the WDT can be cleared.

Time Base time-out period selection. The Time Base time-out period ranges from clock/2

12

to clock/2

15

²Clock²

means the clock source selected by options.

Buzzer output frequency selection. There are eight types of frequency signals for buzzer output: Clock/2

2

~Clock/2

9

.

²Clock² means the clock source selected by options.

Wake-up selection. This option defines the wake-up capability. External I/O pins (PA only) all have the capability to

wake-up the chip from a HALT by a falling edge.