Rainbow Electronics DS25LV02 User Manual

Page 5

DS25LV02: Low-Voltage 1024-Bit EPROM

5 of 17

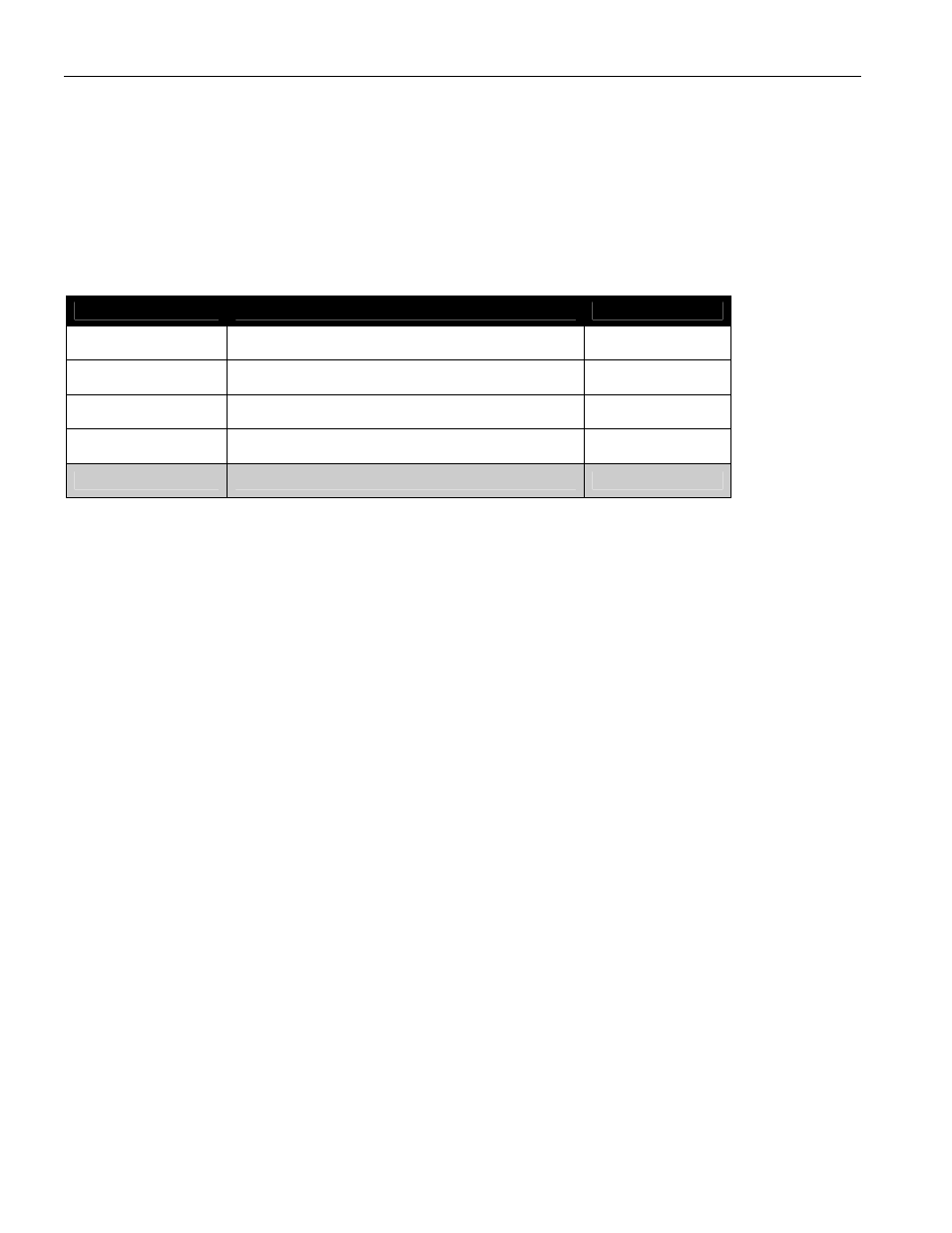

EPROM MEMORY DATA FIELD

The DS25LV02 has a linear address space for access to the EPROM data field. The EPROM data field is

organized as 4 pages of 32 bytes each as shown in Table 1. The Read Memory and Read Data/Generate CRC

Memory function commands provide read access to the 1024 bits of the EPROM data field. The Write Memory

function command provides write access to the EPROM data field. When received from the factory, the entire

1024-bit EPROM data field is erased and returns logical 1’s when read. Bits within the data field are one time

programmable. Programming changes the bit value to logical zero from the factory default erased value of a logical

1. Once a bit is programmed, it cannot be set back to a logical 1.

Table 1. EPROM Data Field

ADDRESS (HEX)

DESCRIPTION

READ/WRITE

0000–001F

PAGE 0 (32 bytes)

R/W*

0020–003F

PAGE 1 (32 bytes)

R/W*

0040–005F

PAGE 2 (32 bytes)

R/W*

0060–007F

PAGE 3 (32 bytes)

R/W*

0080–FFFF

Reserved

* One-time write to “0” for each bit.

READ MEMORY [F0h]

The Read Memory command is used to read data from PAGE 0 to PAGE 3 of the 1024-bit EPROM data field. The

bus master follows the command byte with a 2-byte address (TA1 = (T7:T0), TA2 = (T15:T8)) that indicates a

starting byte location within the data field. An 8-bit CRC of the command byte and address bytes is computed by

the DS25LV02 and read back by the bus master to confirm that the correct command word and starting address

were received. If the CRC is deemed to be incorrect by the bus master, the bus master should issue a reset pulse

and repeat the entire sequence. If the CRC is deemed to be correct by the bus master, read time slots can be

issued to receive data from the EPROM data field starting at the initial address. The bus master can issue a reset

pulse at any point or continue to issue read time slots until the end of PAGE 3 of the data field is reached.

If reading continues through the end of PAGE 3, the bus master can issue eight additional read time slots and the

DS25LV02 will respond with a 8-bit CRC of all data bytes read from the initial starting byte through the last byte of

PAGE 3. Terminating the command transaction with a reset pulse prior to reaching the end of PAGE 3 results in a

loss of availability of the 8-bit CRC.

READ DATA/GENERATE 8-BIT CRC [C3h]

The Read Data/Generate 8-bit CRC command is used to read data from PAGE 0 to PAGE 3 of the 1024-bit

EPROM data field. The bus master follows the command byte with a 2-byte address

(TA1 = (T7:T0), TA2 = (T15:T8)) that indicates a starting byte location within the data field. An 8-bit CRC of the

command byte and address bytes is computed by the DS25LV02 and read back by the bus master to confirm that

the correct command word and starting address were received. If the CRC is deemed to be incorrect by the bus

master, the bus master should issue a reset pulse and repeat the entire sequence. If the CRC is deemed to be

correct by the bus master, read time slots can be issued to receive data from the EPROM data field starting at the

initial address. The bus master can issue a reset pulse at any point or continue to issue read time slots until the

end of the 32-byte page is reached. If reading occurs through the end of the 32-byte page, the bus master can

issue eight additional read time slots and the DS25LV02 will respond with an 8-bit CRC of all data bytes read from

the initial starting byte through the last byte of the current page. After the CRC is received, additional read time

slots return data starting with the first byte of the next page. This sequence will continue until the bus master reads

PAGE 3 and its accompanying CRC. Thus each page of data can be considered to be 33 bytes long: the 32 bytes

of user-programmed EPROM data and an 8-bit CRC that gets generated automatically at the end of each page.

The Read Data/Generate 8-Bit CRC command sequence can be exited at any point by issuing a reset pulse.