Rainbow Electronics MAX9656 User Manual

Page 8

MAX9655/MAX9656

Low-Power Video Switches

for Dual SCART Connectors

8

_______________________________________________________________________________________

The incoming video signals can have any DC bias

because the input sync-tip clamps restore the

DC level. The output amplifiers have a gain of 2V/V.

The MAX9655/MAX9656 operate from a single 3.3V

supply and consume low quiescent power and low

average power. In addition, the MAX9656 also has

shutdown mode.

Operating Modes

TV_SEL controls whether the encoder or VCR video sig-

nals are sent to the TV SCART. See Table 1.

On the MAX9656, VCR_SEL controls whether the CVBS

signal from the TV SCART or the encoder is sent to the

VCR SCART. SHDN controls whether the device is on

or off. See Tables 2 and 3. In shutdown, the outputs of

the MAX9656 are high impedance.

Input

Every video signal must be AC-coupled to the

MAX9655/MAX9656 through 0.1µF capacitors. The

MAX9655/MAX9656 have sync-tip clamps and bias cir-

cuits to restore the DC level of the video signal after the

input coupling capacitor. When a video input is select-

ed, the input has a sync-tip clamp, which accepts

video signals that have sync pulses or that reach their

minimum level during sync. Composite video with

blanking and sync (CVBS) is an example of a video sig-

nal with sync pulses. The red, green, and blue signals

in an RGBS signal set are examples of signals that

return to their blank level during sync. The sync-tip volt-

age is internally set to 300mV.

When a video input is not selected, the inputs to the

MAX9655 and the MAX9656 do not distort the video

signal in case the video source is driving video signals

to another video circuit such as a video multiplexer.

The inputs are biased at V

DD

/3, which is sufficiently

above ground so that the ESD diodes never forward

bias as the video signal changes. The input resistance

is 220k

Ω, which presents negligible loading on the

video current DAC. The sole exception to this condition

is ENC_CVBS_IN (MAX9655), in which the input circuit

is always a sync-tip clamp. Table 4 summarizes which

input circuit is active on the inputs of the MAX9655

depending on TV_SEL. Table 5 summarizes which input

circuit is active on the inputs of the MAX9656 depend-

ing on TV_SEL and VCR_SEL.

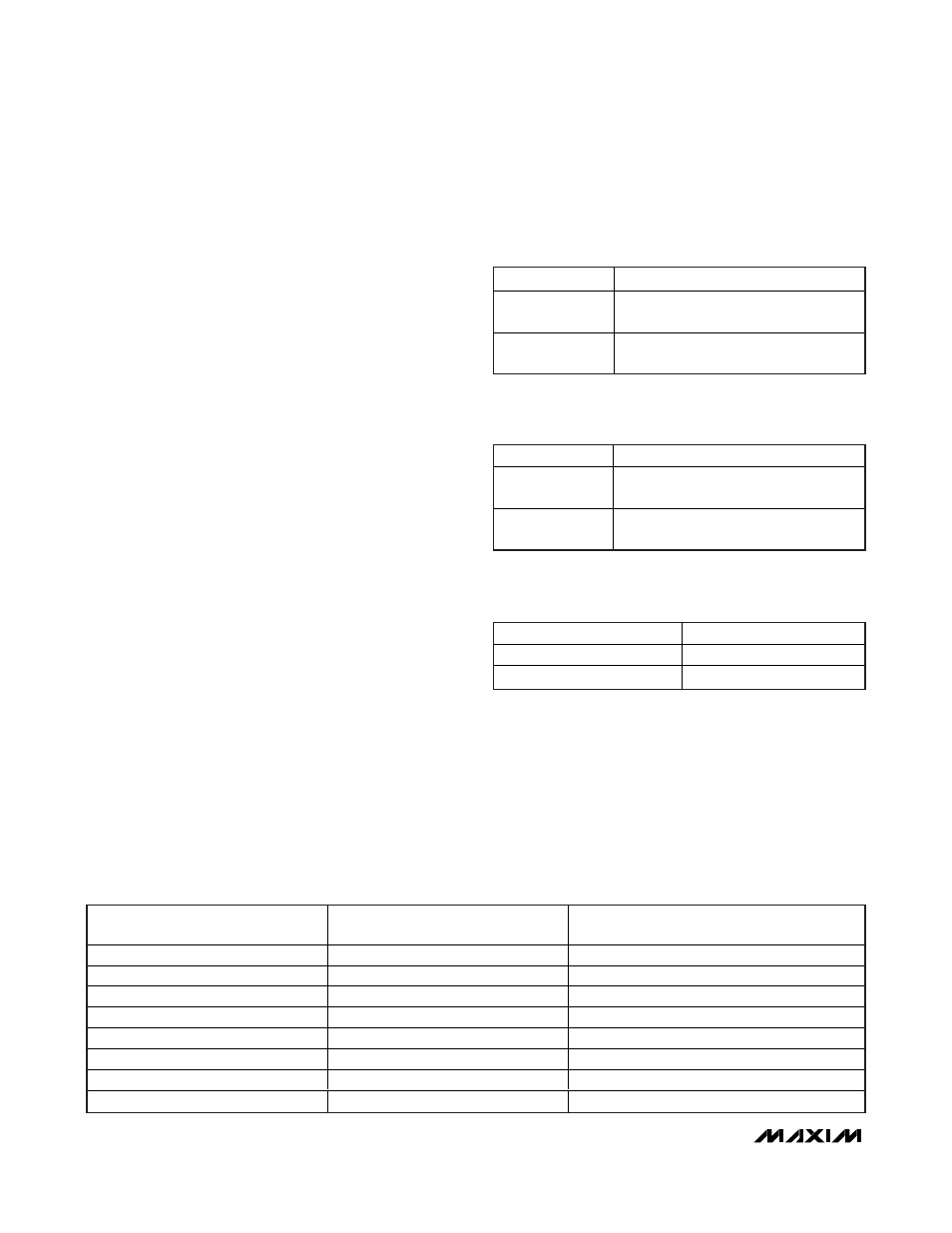

LOGIC STATE

MODE

Low

Encoder video signals are routed to the

TV SCART.

High

VCR SCART video signals are routed to

the TV SCART.

Table 1. TV_SEL Logic (Applicable to

Both the MAX9655 and the MAX9656)

LOGIC STATE

MODE

Low

CVBS signal from encoder is routed to the

VCR SCART.

High

CVBS signal from the TV SCART is routed

to the VCR SCART.

Table 2. VCR_SEL Logic (Only Applicable

to the MAX9656)

LOGIC STATE

MODE

Low

Off

High

On

Table 3.

SHDN Logic (Only Applicable to

the MAX9656)

INPUT

INPUT CIRCUIT

(TV_SEL = LOW)

INPUT CIRCUIT

(TV_SEL = HIGH)

ENC_B_IN

Sync-tip clamp

Bias

ENC_G_IN

Sync-tip clamp

Bias

ENC_R_IN

Sync-tip clamp

Bias

ENC_CVBS_IN

Sync-tip clamp

Sync-tip clamp

VCR_B_IN

Bias

Sync-tip clamp

VCR_G_IN

Bias

Sync-tip clamp

VCR_R_IN

Bias

Sync-tip clamp

VCR_CVBS_IN

Bias

Sync-tip clamp

Table 4. MAX9655 Input Circuit of Input as Determined by State of TV_SEL