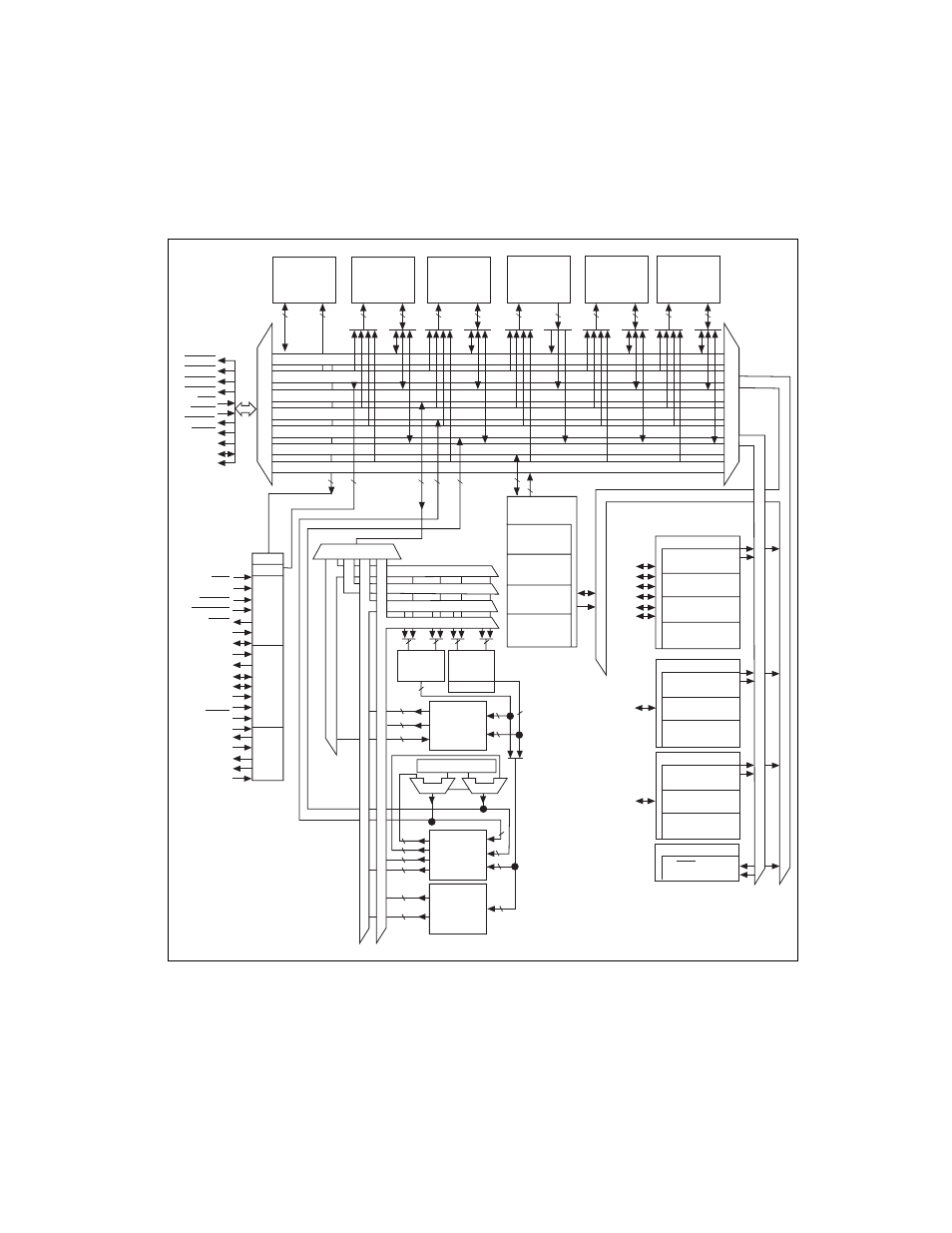

Figure 2-2. vc33 dsp functional block diagram – National Instruments Signal Processing Engineering Educational Device NI SPEEDY-33 User Manual

Page 15

Chapter 2

NI SPEEDY-33 Functional Description and Interface

© National Instruments Corporation

2-3

Figure 2-2 shows the architectural details of the VC33 DSP.

Figure 2-2. VC33 DSP Functional Block Diagram

Cache

(64 x 32)

Cache

(64 x 32)

Cache

(64 x 32)

RAM

Block 0

(1 k x 32)

Cache

(64 x 32)

Cache

(64 x 32)

Boot

Loader

Cache

(64 x 32)

Cache

(64 x 32)

RAM

Block 1

(1 k x 32)

RAM

Block 2

(16 k x 32)

RAM

Block 3

(16 k x 32)

32

32

32

24

24

32

24

24

24

24

32

24

32

24

32

24

32

24

32

PDATA Bus

PADDR Bus

DDATA Bus

DADDR1 Bus

DADDR2 Bus

DMADATA Bus

DMAADDR Bus

MUX

PAGE0

PAGE1

PAGE2

PAGE3

RDT

HOLD

HOLDA

STRB

RW

D31-D0

A23-A0

RSW0,1

SHZ

EDGEMODE

RESET

INT(3–0)

IACK

MCBL/NP

XF(1,0)

TDI

TDO

EMU0

ENU1

TCK

TMS

TRST

EXTCLK

XOUT

XIH

H1

H3

CLKND(0,1)

MUX

IR

PC

Controller

JT

A

G

Em

u

la

tion

PLL CLK

CPU1

CPU1

MUX

32

32

32

40

40

40

40

40

40

40

Multiplier

32-Bit

Barrel

Shifter

ALU

Extended-

Precision

Register

(R7-R0)

40

32

DISP0, IR0, IR1

ARAU1

BK

ARAU0

24

24

32

32

32

24

24

32

32

32

Auxiliary

Registers

(AR0-AR7)

Other

Registers

(12)

DMA Controller

Global-Control

Register

Serial-Port-Control

Register

Source-Address

Register

Destination-

Address Register

Transfer-Counter

Register

Receive/Transmit

(R/X) Timer Register

Data-Transmit

Register

Data-Receive

Register

Serial Port 0

Peripheral Data Bus

Global-Control

Register

Timer-Period

Register

Timer-Counter

Register

Timer 0

Global-Control

Register

Timer-Period

Register

Timer-Counter

Register

Timer 1

STRB-Control

Register

Port Control

FSX0

DX0

CLKX0

FSR0

DR0

CLKR0

TCLK1

TCLK0

CPU2

REG1

REG2

Pe

ri

p

h

e

ra

l Addre

ss

B

us

P

e

ri

pher

a

l D

a

ta

B

us

REG1