Scheduler pipeline, Scheduler pipeline -5 – National Instruments AutoCode NI MATRIX User Manual

Page 215

Chapter 8

AutoCode Sim Cdelay Scheduler

© National Instruments Corporation

8-5

Scheduler Pipeline section that these latencies are caused by the single

posting stage per scheduler invocation in the default AutoCode scheduler,

and by the output posting policy assigned to enabled blocks in the default

scheduler.

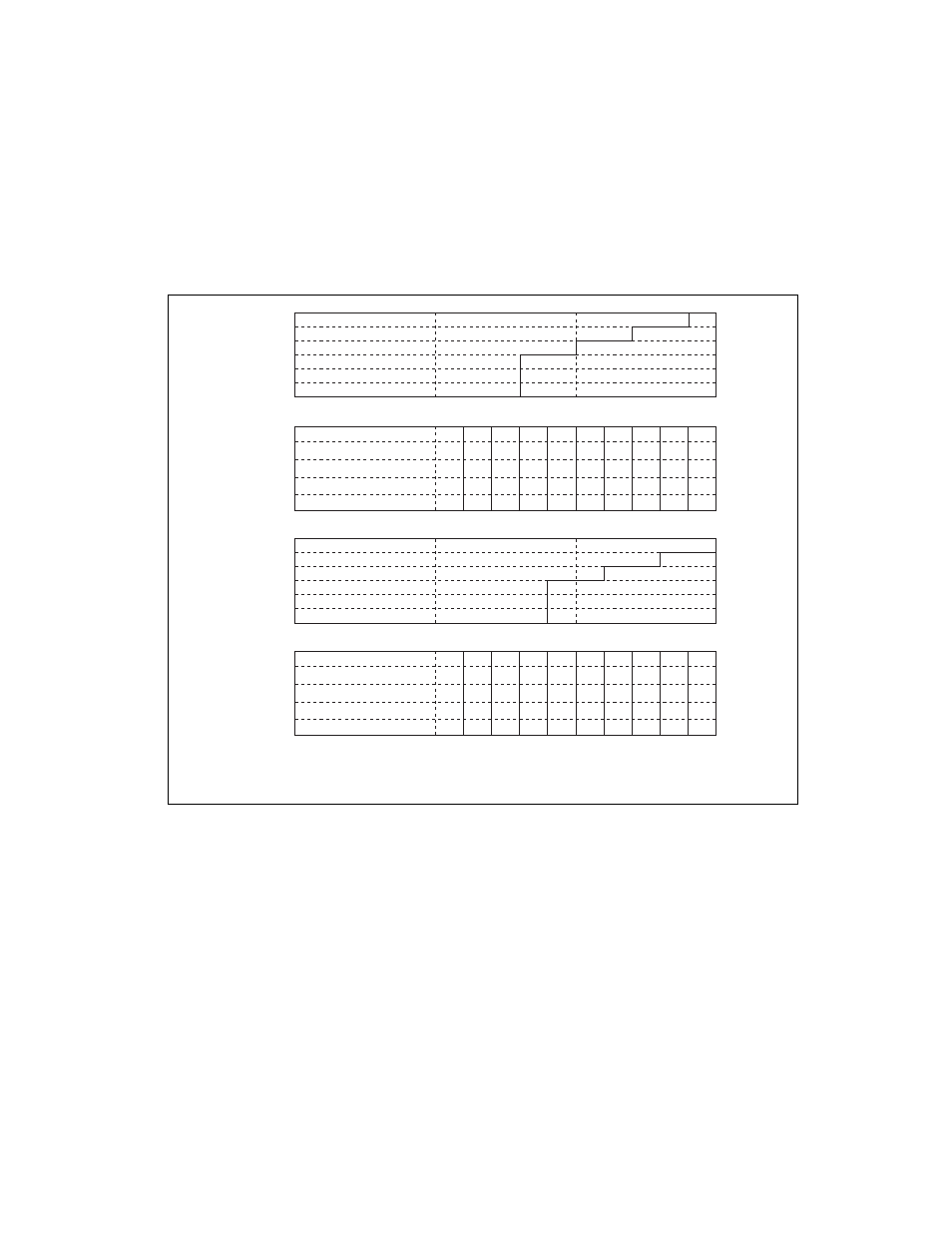

Figure 8-2. Latencies Present in Default AutoCode Scheduler

Scheduler Pipeline

To understand these latencies, you need to know what operations are

performed during each scheduler invocation under the default scheduler.

These are best presented in the form of a pipeline diagram as shown in

Figure 8-3. Stage A resets the priority associated with each DataStore

register so that anyone can write to it. Stage B is where any interpolation

occurs to generate internally needed timepoints from an irregularly-spaced

input vector. In stage C, tasks whose launch times have arrived or whose

Time

0

0.5

1

1.5

0

0.2

0.4

0.6

0.8

1

0

0.2

0.4

0.6

0.8

1

0

0.2

0.4

0.6

0.8

1

1.2

0

0.2

0.4

0.6

0.8

1

1.2

enab_signal

enab_sb_out

T

rigger Signal

tr

ig_sb_out