Imr - interrupt mask register, Ctur and ctlr - counter/timer registers, Imr – interrupt mask register – Philips SCC2691 User Manual

Page 15: Ctur and ctlr – counter/timer registers

Philips Semiconductors

Product data sheet

SCC2691

Universal asynchronous receiver/transmitter (UART)

2006 Aug 04

15

IMR – Interrupt Mask Register

The programming of this register selects which bits in the ISR cause an

interrupt output. If a bit in the ISR is a ‘1’ and the corresponding bit in

the IMR is a ‘1’, the INTRN output is asserted (low). If the corresponding

bit in the IMR is a zero, the state of the bit in the ISR has no effect on

the INTRN output. Note that the IMR does not mask reading of the ISR.

NOTE: When IMR[6] is a 1, a 1 on the MPI pin causes and interrupt.

CTUR and CTLR – Counter/Timer Registers

The CTUR and CTLR hold the eight MSBs and eight LSBs,

respectively, of the value to be used by the counter/timer in either

the counter or timer modes of operation. The minimum value which

may be loaded is H‘0002’.

In the timer (programmable divider) mode, the C/T generates a

square wave whose period is twice the value (in clock periods) of

the CTUR and CTLR. The waveform so generated is often used for

a data clock. The formula for calculating the divisor n to load to the

CTUR and CTLR for a particular 1X data clock is shown below:

n

+

C

ń

T Clock Frequency

2 x 16 x Baud rate desired

Often this division will result in a non-integer number; 26.3, for

example. One can only program integer numbers in a digital divider.

Therefore, 26 would be chosen. This gives a baud rate error of

0.3/26.3 which is 1.14%; well within the ability asynchronous mode

of operation.

If the value in CTUR or CTLR is changed, the current half-period will

not be affected, but subsequent half-periods will be.

The counter ready status bit (ISR[4]) is set once each cycle of the

square wave. The bit is reset by a stop counter command. The

command, however, does not stop the C/T. The generated square

wave is output on MPO if it is programmed to be the C/T output.

In the counter mode, the C/T counts down the number of pulses

loaded in CTUR and CTLR. Counting begins upon receipt of a start

C/T command. Upon reaching the terminal count, the counter ready

interrupt bit (ISR[4]) is set. the counter continues counting past the

terminal count until stopped by the CPU. If MPO is programmed to

be the output of the C/T, the output remains high until the terminal

count is reached, at which time it goes low.

The output returns to the high state and ISR[4] is cleared when the

counter is stopped by a stop counter command. The CPU may

change the values of CTUR and CTLR at any time, but the new

count becomes effective only on the next start counter command. If

new values have not been loaded, the previous values are

preserved and used for the next count cycle.

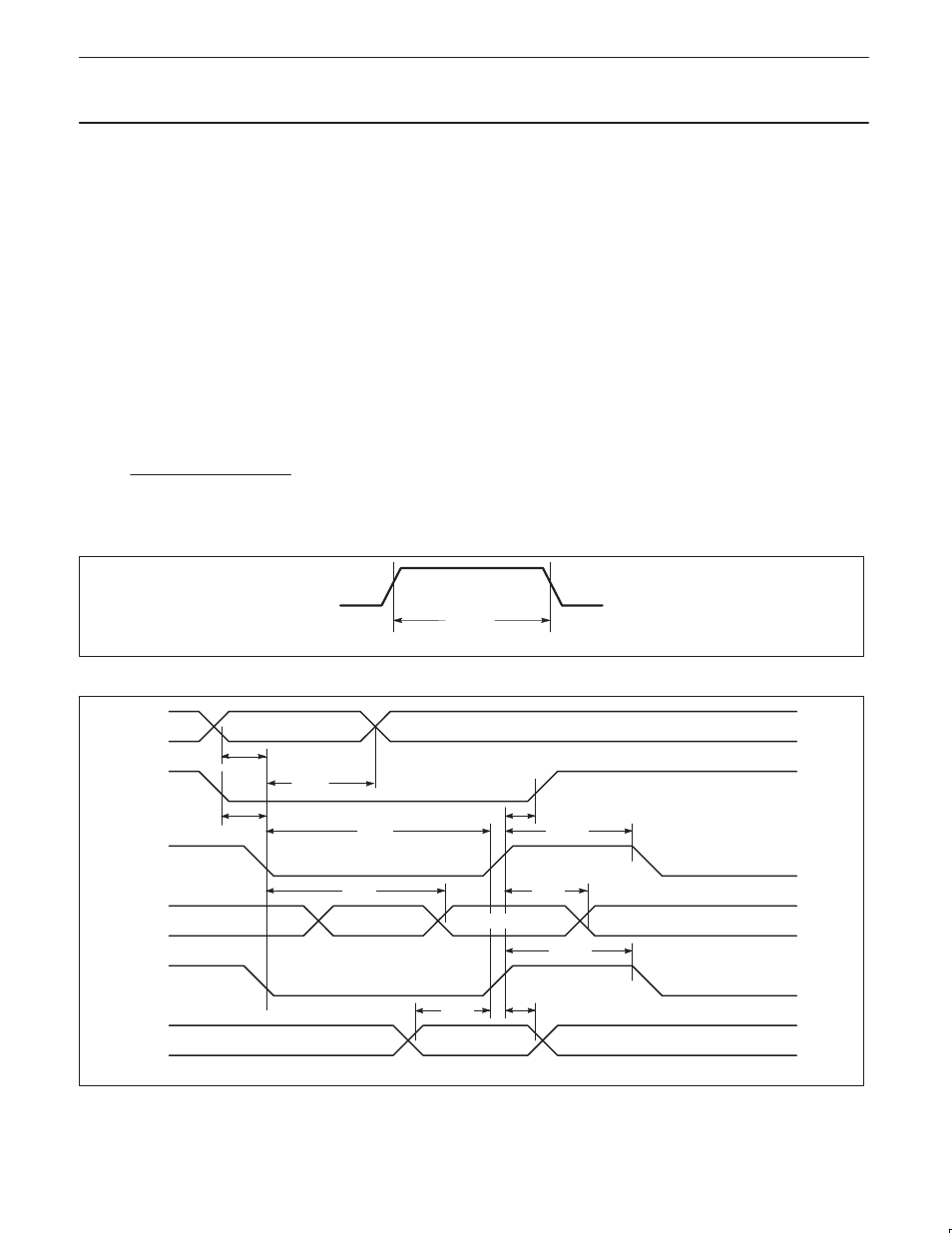

SD00028

RESET

t

RES

Figure 3. Reset Timing

A0–A2

CEN

RDN

D0–D7

(READ)

WRN

D0–D7

(WRITE)

t

AS

t

AH

t

CS

t

RWD

t

DD

t

DF

t

RWD

t

DH

t

DS

t

RW

t

CH

FLOAT

FLOAT

NOT VALID

VALID

VALID

SD00124

Figure 4. Bus Timing