Sr- channel status register, Acr - auxiliary control register – Philips SCC2691 User Manual

Page 13

Philips Semiconductors

Product data sheet

SCC2691

Universal asynchronous receiver/transmitter (UART)

2006 Aug 04

13

CR[1] – Disable Receiver

This command terminates operation of the receiver immediately; a

character being received will be lost. The command has no effect on

the receiver status bits or any other control registers. If the special

wake-up mode is programmed, the receiver operates even if it is

disabled (see Wake-up Mode).

CR[0] – Enable Receiver

Enables operation of the receiver. If not in the special wake-up

mode, this also forces the receiver into the search for start bit state.

SR – Channel Status Register

The status register is updated while RDN is negated. Therefore, the

bus interface used with this device must not use a static RDN line.

The RDN line must be pulsed to allow status register updates.

SR[7] – Received Break

This bit indicates that an all zero character of the programmed

length has been received without a stop bit. Only a single FIFO

position is occupied when a break is received; further entries to the

FIFO are inhibited until the RxD line returns to the marking state for

at least one half bit time two successive edges of the internal or

external 1X clock. This will usually require a high time of one X1

clock period or 3 X1 edges since the clock of the controller is

not synchronous to the X1 clock.

When this bit is set, the change in break bit in the ISR (ISR[3]) is

set. ISR[3] is also set when the end of the break condition, as

defined above, is detected.

The break detect circuitry is capable of detecting breaks that

originate in the middle of a received character. However, if a break

begins in the middle of a character, it must last until the end of the

next character time in order for it to be detected.

SR[6] – Framing Error (FE)

This bit, when set, indicates that a stop bit was not detected when

the corresponding data character in the FIFO was received. The

stop bit check is made in the middle of the first stop bit position.

SR[5]– Parity Error (PE)

This bit is set when the with parity or force parity mode is

programmed and the corresponding character in the FIFO was

received with incorrect parity. In special wake-up mode, the parity

error bit stores the received A/D bit.

SR[4] – Overrun Error (OE)

This bit, when set, indicates that one or more characters in the

received data stream have been lost. It is set upon receipt of a new

character when the FIFO is full and a character is already in the

receive shift register waiting for an empty FIFO position. When this

occurs, the character in the receive shift register (and its break

detect, parity error and framing error status, if any) is lost. This bit is

cleared by a reset error status command.

SR[3] – Transmitter Empty (TxEMT)

This bit will be set when the transmitter underruns, i.e., both the

TxEMT and TxRDY bits are set. This bit and TxRDY are set when

the transmitter is first enabled and at any time it is re-enabled after

either (a) reset, or (b) the transmitter has assumed the disabled

state. It is always set after transmission of the last stop bit of a

character if no character is in the THR awaiting transmission.

It is reset when the THR is loaded by the CPU, a pending

transmitter disable is executed, the transmitter is reset, or the

transmitter is disabled while in the underrun condition.

SR[2] – Transmitter Ready (TxRDY)

This bit, when set, indicates that the THR is empty and ready to be

loaded with a character. This bit is cleared when the THR is loaded

by the CPU and is set when the character is transferred to the

transmit shift register. TxRDY is reset when the transmitter is

disabled and is set when the transmitter is first enabled, e.g.,

characters loaded in the THR while the transmitter is disabled will

not be transmitted.

SR[1] – FIFO Full (FFULL)

This bit is set when a character is transferred from the receive shift

register to the receive FIFO and the transfer causes the FIFO to

become full, i.e., all three FIFO positions are occupied. It is reset

when the CPU reads the FIFO and there is no character in the

receive shift register. If a character is waiting in the receive shift

register because the FIFO is full, FFULL will be reset by the CPU

read and then set by the transfer of the character to the FIFO, which

causes all three FIFO positions to be occupied.

SR[0] – Receiver Ready (RxRDY)

This bit indicates that a character has been received and is waiting

in the FIFO to be read by the CPU. It is set when the character is

transferred from the receive shift register to the FIFO and reset

when the CPU reads the RHR, and no more characters are in the

FIFO.

ACR – Auxiliary Control Register

ACR[7] – Baud Rate Generator Set Select

This bit selects one of two sets of baud rates generated by the BRG.

Set 1:

50, 110, 134.5, 200, 300, 600, 1.05k, 1.2k, 2.4k, 4.8k, 7.2k,

9.6k, and 38.4k baud.

Set 2:

75, 110, 134.5, 150, 300, 600, 1.2k, 1.8k, 2.0k, 2.4k, 4.8k,

9.6k, and 19.2k baud.

The selected set of rates is available for use by the receiver and

transmitter. See Table 3 for characteristics of the BRG.

ACR[6:4] – Counter/Timer Mode and Clock Source Select

This field selects the operating mode of the counter/timer and its

clock source as follows:

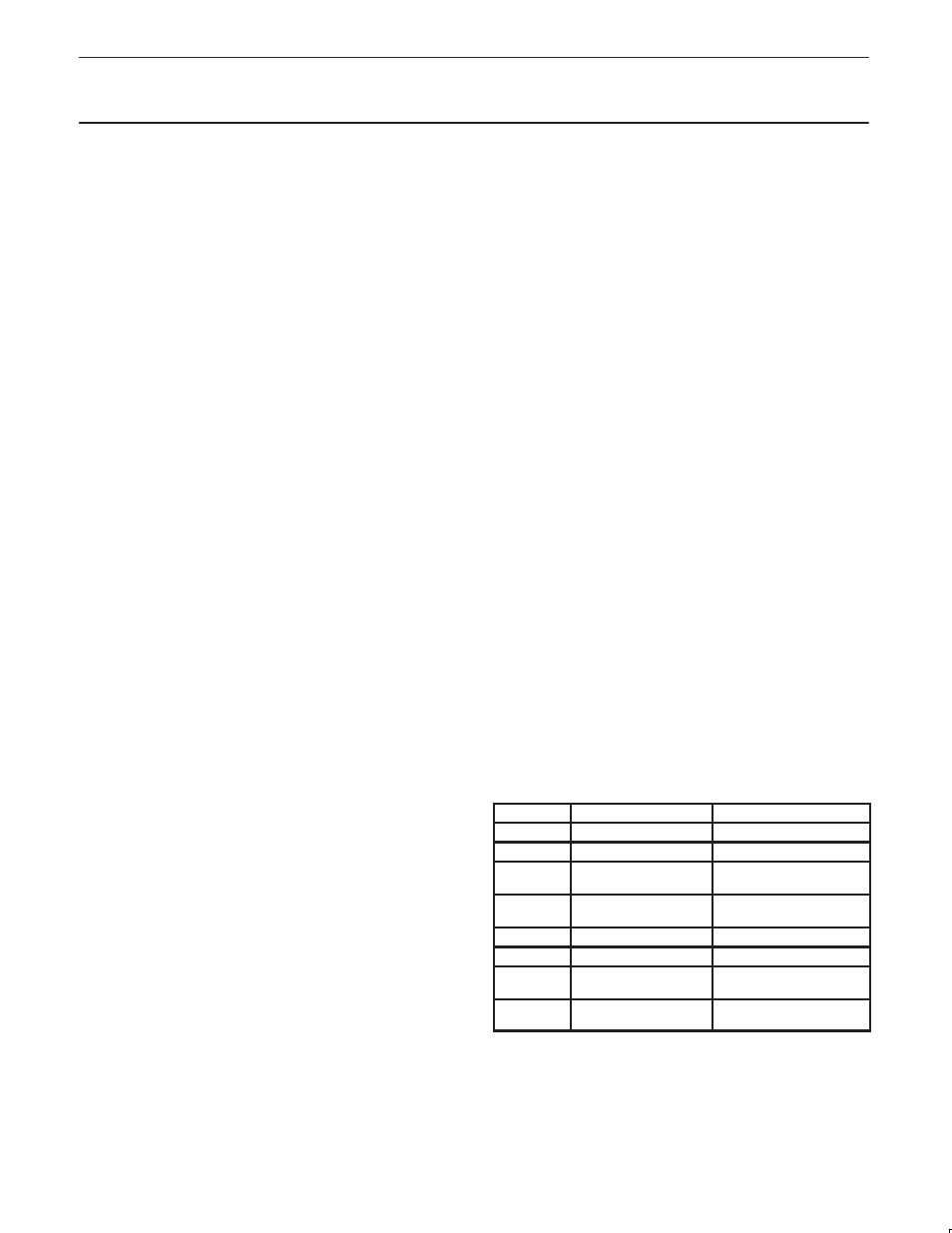

Table 4. ACR[6:4] Operating Mode

ACR [6:4]

Mode

Clock Source

0 0 0

Counter

MPI pin

0 0 1

Counter

MPI pin divided by 16

0 1 0

Counter

TxC–1X clock of the

transmitter

0 1 1

Counter

Crystal or X1/CLK divided

by 16

1 0 0

Timer (square wave)

MPI pin

1 0 1

Timer (square wave)

MPI pin divided by 16

1 1 0

Timer (square wave)

Crystal or external clock

(X1/CLK)

1 1 1

Timer (square wave)

Crystal or X1/CLK divided

by 16

The timer mode generates a squarewave.

ACR[3] – Power-Down Mode Select

This bit, when set to zero, selects the power-down mode. In this

mode, the SCC2691 oscillator is stopped and all functions requiring

this clock are suspended. The contents of all registers are saved. It

is recommended that the transmitter and receiver be disabled prior