1 register description, Tea5880ts, Philips semiconductors – Philips TEA5880TS User Manual

Page 9

9397 750 13022

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data sheet

Rev. 02 — 26 April 2004

9 of 27

Philips Semiconductors

TEA5880TS

Integrated FM stereo radio IC for host processor tuning

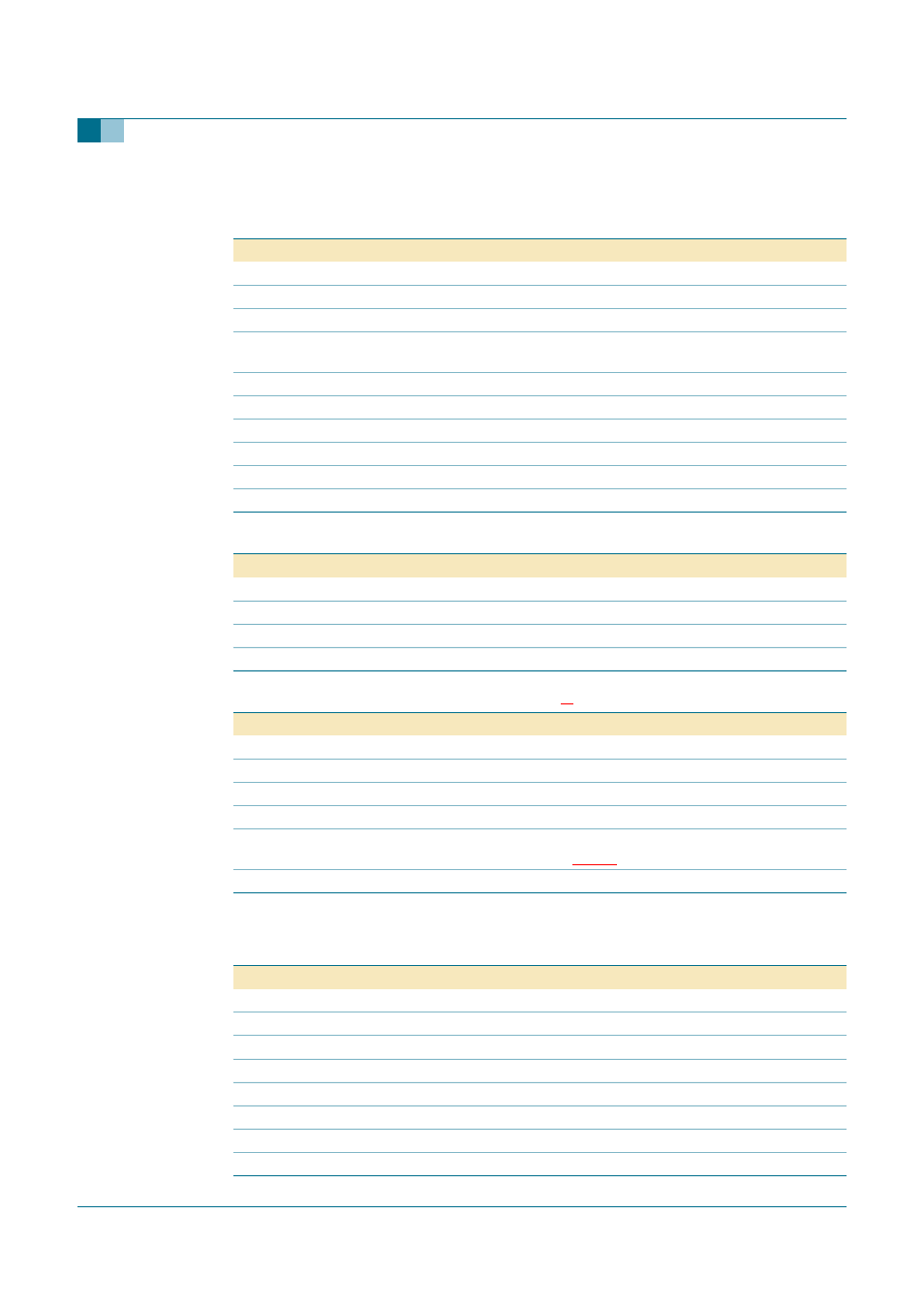

8.1 Register description

[1]

The application should write logic 0 to this register at start-up to ensure that the device functions correctly.

Table 5:

TEA5880TS registers description

Address

Register name

Access

Operation

Data width

Clocks

0000b

VADC

write only

VADC register

11 bits

15

0001b

CTRL_C

write only

control register C

11 bits

15

0010b

CTRL_A

write only

control register A

11 bits

15

0011b

OSC_STEREO

write only

oscillator stereo

decoder clock

11 bits

15

0100b

CTRL_B

write only

control register B

11 bits

15

0101b

CAP_FM

write only

capacitor bank FM

11 bits

15

0110b

OSC_IF

write only

oscillator IF

11 bits

15

0111b

OSC_FM

write only

oscillator FM

11 bits

15

-

STATUS

read only

status register

16 bits

15

-

COUNTER

read only

counter register

16 bits

15

Table 6:

VADC - (address 0h) bit description

Bit

Symbol

Description

14 to 11

-

address bits

10 to 6

VADC2[4:0]

controls the width filter

5

-

not applicable; should be written to logic 0

4 to 0

VADC1[4:0]

controls the center filter

Table 7:

CTRL_C - (address 1h) bit description

Bit

Symbol

Description

14 to 11

-

address bits

10 and 9

-

reserved for production test; should be written to logic 0

8

-

reserved for swapping counters1 and 2; should be written to logic 0

7 to 4

-

not applicable; should be written to logic 0

3 to 1

-

reserved for time delay selection (counter 2); application should keep

bits 3 to 1 at logic 0; see

0

-

reserved for enable counter 2; should be written to logic 0

Table 8:

Time delay selection

Value

Decimal

Stop value

000b

0

count 2

001b

1

count 8

010b

2

count 32

011b

3

count 128

100b

4

count 512

101b

5

count 2048

110b

6

count 8192

111b

7

count 32768