Tea5880ts, Philips semiconductors – Philips TEA5880TS User Manual

Page 10

9397 750 13022

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Preliminary data sheet

Rev. 02 — 26 April 2004

10 of 27

Philips Semiconductors

TEA5880TS

Integrated FM stereo radio IC for host processor tuning

[1]

The frequency is decreased when increasing the content of this register.

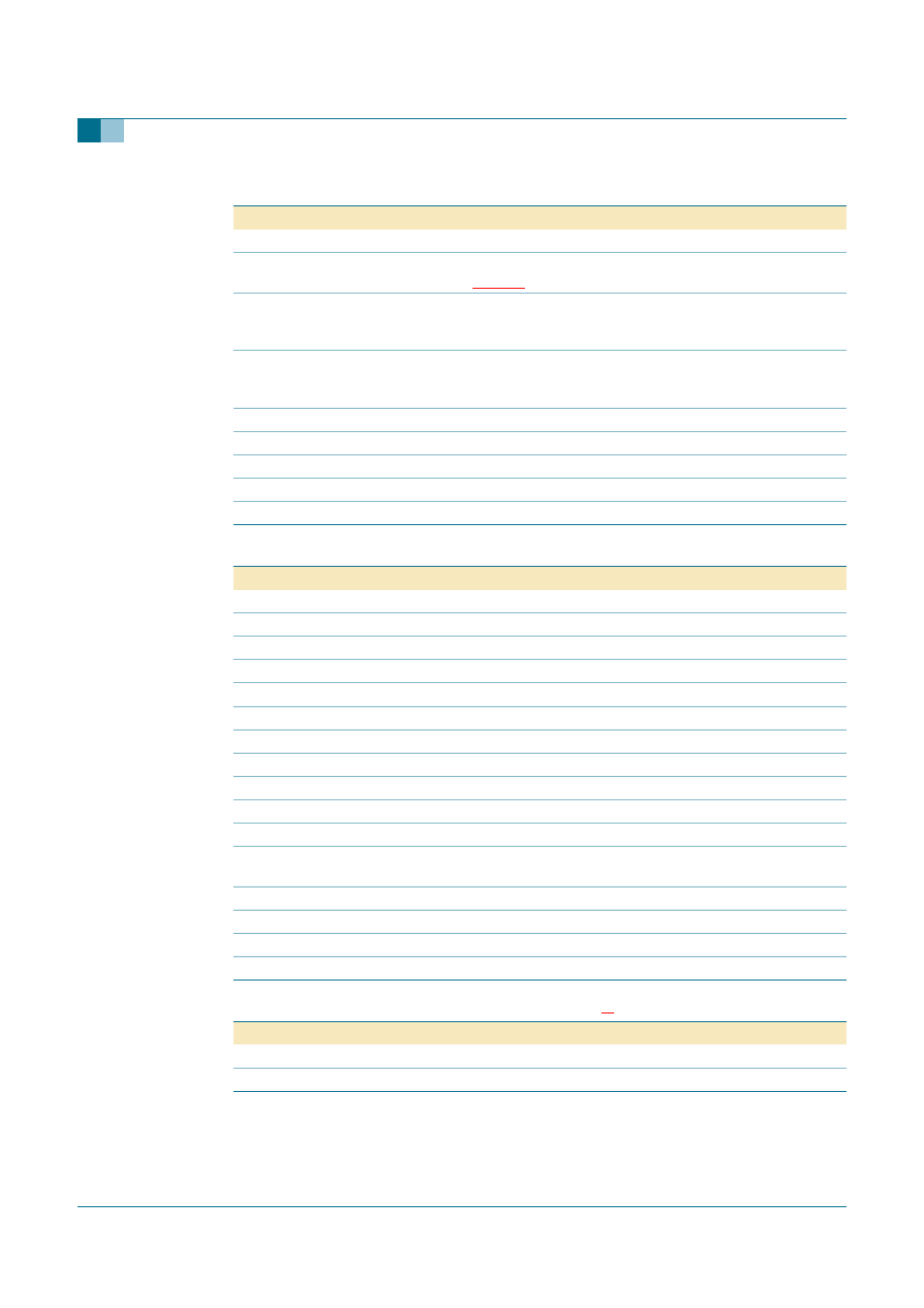

Table 9:

CTRL_A - (address 2h) bit description

Bit

Symbol

Description

14 to 11

-

address bits

10 to 7

OUTPUT_

SELECT[3:0]

selects an internal circuit as output for measurement purpose;

see

6

STE_PMUTE

mutes the stereo PLL when set to logic 1; this bit should be

set during calibration of the stereo decoder clock and should be

cleared during normal operation

5

DEM_PMUTE

mutes the demodulator PLL when set to logic 1; this bit

should be set during calibration of the IF frequency and should

be cleared during normal operation

4

STE_INT_OFF#

turns off the stereo integrator loop when set to logic 0

3

EN_MEAS#

enables measurement when set to logic 0

2

AMUTE

mutes the audio when set to logic 1

1

FM

enables the FM circuitry when set to logic 1

0

-

reserved for AM circuitry; should be written to logic 0

Table 10:

Description of OUTPUT_SELECT bits

Symbol

Value

Decimal

Output selected

OS-NONE

0000b

0

no output selected

OS_FM_OSC

0001b

1

FM oscillator

OS_NA2

0010b

2

not defined

OS_CNT2_RDY_NA

0011b

3

reserved for counter 2 ready output

OS_NA4

0100b

4

not defined

OS_STEREO_DEC

0101b

5

stereo decoder clock

OS_NA6

0110b

6

not defined

OS_STEREO_LED

0111b

7

stereo LED

OS_NA8

1000b

8

not defined

OS_IF_OSC

1001b

9

IF oscillator

OS_INTERRUPT_NA

1010b

10

reserved for interrupt output

OS_PISO

1011b

11

PISO output (reading STATUS / COUNTER

register)

OS_NA12

1100b

12

not defined

OS_RDS_NA

1101b

13

reserved for RDS output

OS_NA14

1110b

14

not defined

OS_NA15

1111b

15

not defined

Table 11:

OSC_STEREO - (address 3h) bit description

Bit

Symbol

Description

14 to 11

-

address bits

10 to 0

SO[10:0]

11-bit digital-to-analog converter for adjusting the stereo decoder clock