Extended control register, Table 27 . extended control register, Ieee 1284 port – Lucent Technologies USS-720 User Manual

Page 46: Instant usb, Ieee

5-20

Lucent Technologies Inc.

USS-720

Instant USB

Preliminary Data Sheet, Rev. 5

USB-to-

IEEE

1284 Bridge

September 1999

13

IEEE 1284 Port

(continued)

Extended Control Register

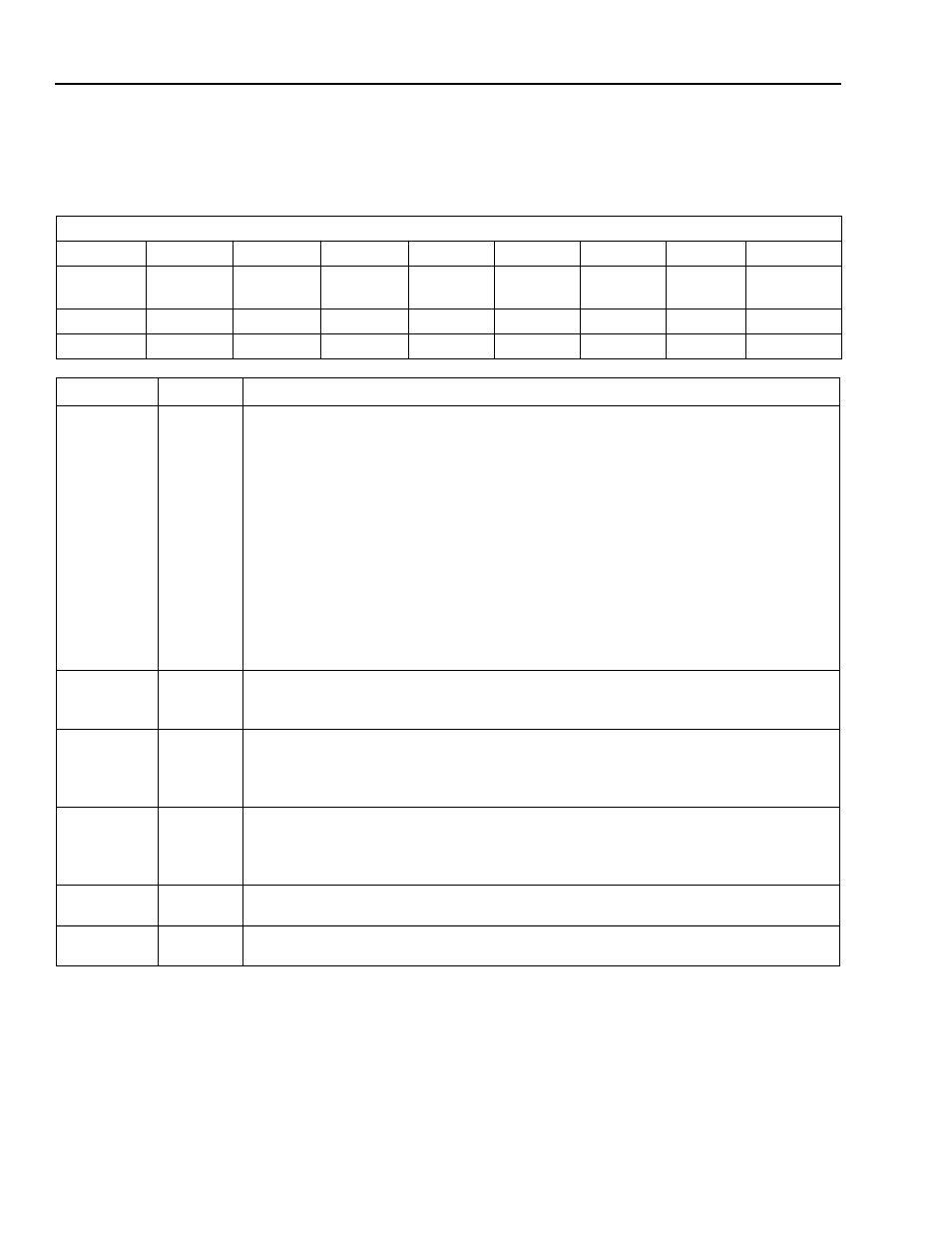

Table 27. Extended Control Register

Extended Control Register

Address: 6

Bit

7

6

5

4

3

2

1

0

Symbol

Mode[2]

Mode[1]

Mode[0]

nAck

interrupt

nFault

interrupt

Bulk In

interrupt

Bulk In

empty

Bulk Out

empty

Access

R/W

R/W

R/W

Read

Read

Read

Read

Read

Default

0

0

0

0

0

0

1

1

Bit

Symbol

Bit Description

7—5

Mode[2:0] Mode. In Register Mode (when Auto Mode is 0), this bit controls the mode of the

parallel port interface. This field is equivalent to the Mode field in a standard host-side

parallel port controller chip. The supported modes are as follows:

Mode[2:0]

Mode

Description

000

Standard Mode

Full software control, data lines are output only

001

Bidirectional Mode

Full software control, data lines are bidirectional

010

Compatibility Mode

Hardware handshaking

011

ECP Mode

Software negotiations, hardware data transfers

100

EPP Mode

Software negotiations, hardware data transfers

101

Reserved

110

Reserved

111

Reserved

For more information, see the Register-Based Operation section on page 14.

4

nAck

Interrupt

nAck Interrupt. This bit will be set when the parallel port nAck signal makes a transi-

tion from 0 to 1 while the Interrupt Enable bit in the Control Register is set to 1. Inter-

rupt status is cleared by any register read.

3

nFault

Interrupt

nFault Interrupt. This bit will be set when the parallel port nFault signal makes a tran-

sition from 1 to 0 while the nFault Interrupt Mask bit in the USS-720 Control Register

is set to 0. An interrupt will also be generated if the mask bit goes low while nFault is

low. Interrupt status is cleared by any register read.

2

Bulk In

Interrupt

Bulk In Interrupt. This bit will be set when Bulk In data is available and the Bulk In

Interrupt Mask bit in the Control Register is set to 0. This allows software to use the

interrupt pipe to automatically receive notification of available Bulk In data rather than

polling with Bulk In requests. Interrupt status is cleared by any register read.

1

Bulk In

Empty

Bulk In Empty. This bit will be clear when there is Bulk In data available for reading

by the host, and set when there is not.

0

Bulk Out

Empty

Bulk Out Empty. This bit will be clear when there is Bulk Out data waiting in the

buffers or in the process of being transmitted over the parallel port, and set otherwise.