9 peer cop health mstr operation, Control block utilization, Peer cop communications health status information – Schneider Optics Web Embedded Server User Manual

Page 45: Peer cop health mstr operation

The MSTR Instruction

840 USE 115 00 Version 1.0

35

3.2.9

Peer Cop Health MSTR Operation

The peer cop health operation (type 9 in the displayed register of the top node)

reads selected data from the peer cop communications health table and loads that

data to specified 4x registers in state RAM. The peer cop communications health

table is12 words long, and the words are indexed via this MSTR operation as words

0 ... 11.

Control Block

Utilization

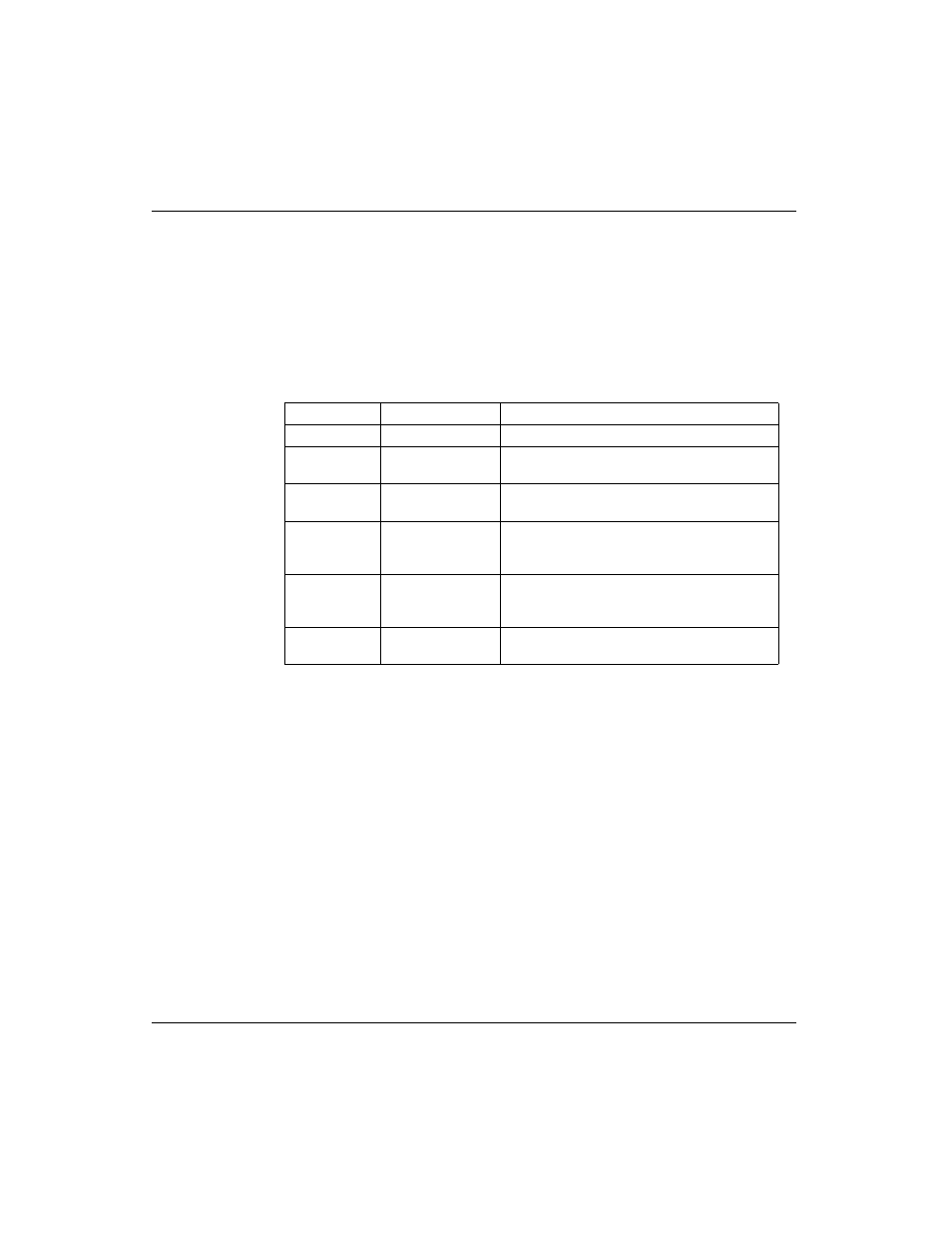

The registers in the MSTR control block (the top node) contain the information for a

Peer Cop Health operation as described in the following table:

Peer Cop

Communications

Health Status

Information

The peer cop communications health table (shown below) comprises 12

contiguous register that can be indexed in an MSTR operation as words 0 ... 11.

Each bit in each of the table words is used to represent an aspect of

communications health relative to a specific node on the TCP/IP network:

z

The bits in words 0 ... 3 represent the health of the global input communication

expected from nodes 1 ... 64. Since global input is not supported these bits are

set to zero.

z

The bits in words 4 ... 7 represent the health of the output from a specific node.

z

The bits in words 8 ... 11 represent the health of the input to a specific node.

Register

Function

Content

Displayed

Operation Type

9

First implied

Error status

Displays a hex value indicating an MSTR error,

when relevant.

Second implied

Data Size

Number of words requested from peer cop table

(range 1 ... 12).

Third implied

Index

First word from the table to be read (range 0 ...

11, where 0 = the first word in the peer cop table

and 11 = the last word in the table).

Fourth implied

Low byte

Quantum backplane slot address of the NOE

module.

Fifth ... Eighth

implied

Destination

Each register contains one byte of the 32-bit IP

address.