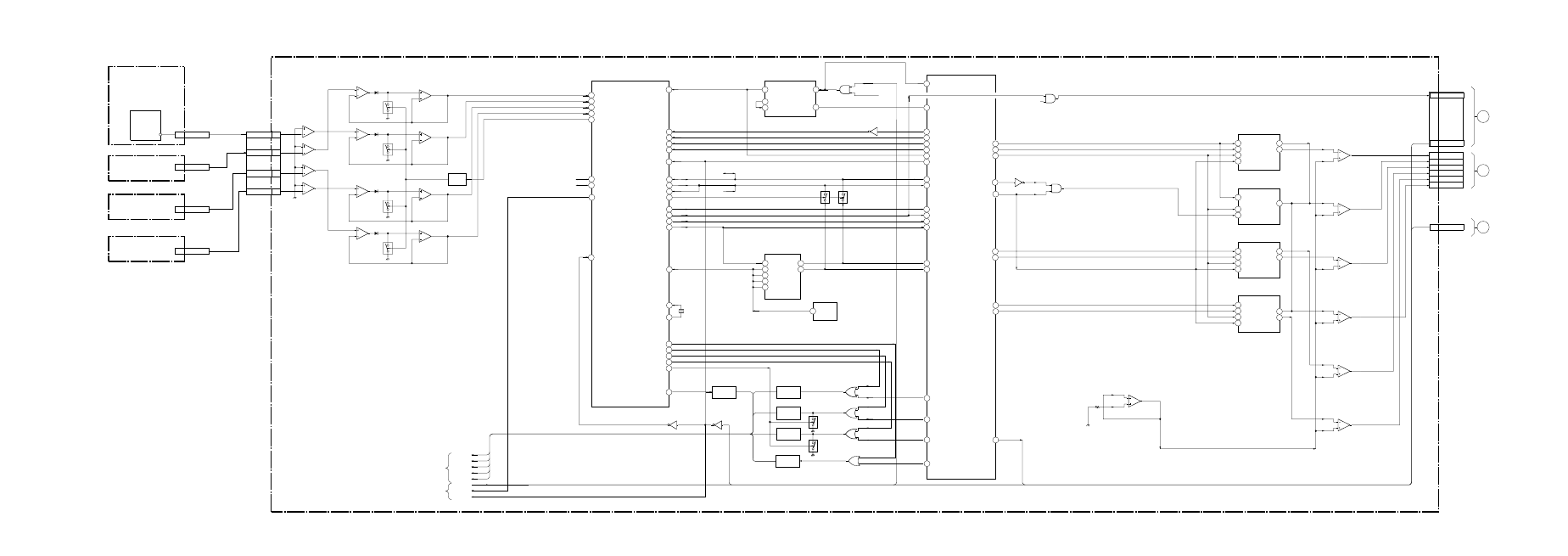

Block diagram (3), Pjed-cpu, regi correcton), Sensor) – Sony KP 48S75 User Manual

Page 54

– 62 –

– 61 –

– 60 –

– 59 –

BLOCK DIAGRAM (3)

18

7

26

27

28

49

47

50

48

44

9

7

8

1

2

6

5

6

3

4

15

30

17

8

11

12

29

18

46

60

28

14

13

26

27

10

9

2

3

5

4

21

44

58

45

59

22

23

25

38

12

5

4

3

12

37

36

32

33

34

35

11

6

46

58

61

62

59

55

8

39

17

16

15

57

15

16

13

6

11

6

11

14

15

15

16

13

14

16

13

15

16

13

6

11

11

14

DF

VP

REGI MUTE

D FOCUS

RH

RV

GH

GV

BH

BV

RSI

LSI

CLK

LRCK

ROUT

LOUT

IC817

R DAC

IC807

BV DAC

IC816

G DAC

IC815

B DAC

LSI

CLK

LRCK

LOUT

RSI

LSI

CLK

LRCK

ROUT

LOUT

RSI

LSI

CLK

LRCK

ROUT

LOUT

IC819

BV-FILTER/BUFF

IC812

(2/4)

INV

IC812

(3/4)

IC808

(4/6)

IC818

CENT REF

RVOUT

RHOUT

BCLK

HBLK OUT

WCLK

GVOUT

GHOUT

BVOUT

BHOUT

DAOUT

DF

HP

IC812

INV(4/4)

HBLK IN

TEST5

PWM2

XOFDEF

XBUSY

XACKM

TEST4

VBLK IN

SCLS

SDAS

XRESET

XMUTE

XSTOP

XWC

SCLM

SDAM

IC814

OSD MIX

ROUT

GOUT

BOUT

YSOUT

+5V

VCO OUT

PFD OUT

VCO IN

FINA

FINB

IC805

PJED-CPU

IC809

PLL

16MHz

WP

VDD

A0

A1

A2

SCLM

SDAM

IC810

EEPROM

RST

IC811

RESET

OR

OB

OI

OG

O YM

O YS

I EXLC

RESET

I OSC

O OSC

I VP

DREG SCL

O DREG SDA

I DREG SDA

O IIC SW

O DREGI RST

O DREGI MUTE

O KUMUPRT

O NVM STOP

MAIN SCL

I AREGI D0

I AREGI D1

I AREGI D2

I AREGI D3

O AREG RST

MAIN SDA

BINT

I VPULSE

CN801

(2/2)

CN402

CN202(1)

IC803

DIGITAL REGI

PSCL

PSDA

I HP

I DREG OVF

I DREG BSY

I DREG ACK

LEFT

UPPER

LOWER

RIGHT

S3001

SENSOR

CN3001

CN802

Q804

Q803

Q802

SW

Q801

RE-YM

RE-YS

RE-R

RE-G

3

1

2

6

4

5

11

13

12

8

9

10

RE-B

VP

YM OR

Q806

R OR

Q807

G OR

Q809

Q811

ATT

Q812

ATT

B OR

Q808

YS OR

Q813

Q805

1

1

1

2

3

1

2

3

1

2

3

7

6

5

7

6

5

7

5

6

8

9

10

8

9

10

8

9

10

14

13

12

14

13

12

14

IC808

(2/6)

3

4

IC808

(5/6, 6/6)

13

10

13

12

3

5

7

SENSOR

LEFT

UPPER

LOWER

RIGHT

SCL

SDA

RE-R

RE-G

RE-B

RE-YM

RE-YS

HP

B INT

VP-BUFF

2

1

7

6

5

3

IC801

IC808

(1/6, 3/6)

1

6

11

12

13

9

9

10

8

8

5

D+5V

6

4

7

2

3

IC822

GH-FILTER/BUFF

7

2

3

IC820

BH-FILTER/BUFF

7

2

3

IC821

GV-FILTER/BUFF

7

2

3

IC823

RV-FILTER/BUFF

7

2

3

IC824

RH-FILTER/BUFF

7

2

3

1

3

10

9

7

5

3

1

VP

4

(PJED-CPU, REGI CORRECTON)

KP-48-53-61V80 -BD-6-M

1

2

3

REGI OUT

+5V

X801

12MHz

IC802

IV CONV

IC804

PEAK HOLD

IC806

BUFF

L

TO G

BOARD

CN1502

M

TO G

BOARD

CN651

N

TO G

BOARD

CN501

A

(SENSOR)

S

(SENSOR)

S

(SENSOR)

S

(SENSOR)

S

(4/4)

TO A BOARD

VIDEO

BLOCK

TO A BOARD

SYSTEM CONTROL

BLOCK