7 reference clock, Table 4.2 refclk modes, Reference clock – SMSC FlexPWR LAN8720 User Manual

Page 26: Datasheet

Small Footprint RMII 10/100 Ethernet Transceiver with HP Auto-MDIX Support

Datasheet

Revision 1.0 (05-28-09)

26

SMSC LAN8720/LAN8720i

DATASHEET

CRS_DV toggles at 25 MHz in 100Mb/s mode and 2.5 MHz in 10Mb/s mode when CRS ends before

RXDV (i.e. the FIFO still has bits to transfer when the carrier event ends.) Therefore, the MAC can

accurately recover RXDV and CRS.

During a false carrier event, CRS_DV shall remain asserted for the duration of carrier activity. The data

on RXD[1:0] is considered valid once CRS_DV is asserted. However, since the assertion of CRS_DV

is asynchronous relative to REF_CLK, the data on RXD[1:0] shall be “00” until proper receive signal

decoding takes place.

4.7

Reference Clock

The LAN8720 is designed to operate in one of two available modes as shown in

During start-up, the LAN8720 monitors the LED2/nINTSEL pin to determine which mode has been

configured as described in

.

In the first mode, the 50MHz REF_CLK is driven on the XTAL1/CLKIN pin. This is the traditional

system configuration when using RMII, and is described in

. In the second mode, an

advanced feature of the LAN8720 allows a low-cost 25MHz crystal to be used as the reference for

REF_CLK. This configuration may result in reduced system cost and is described in

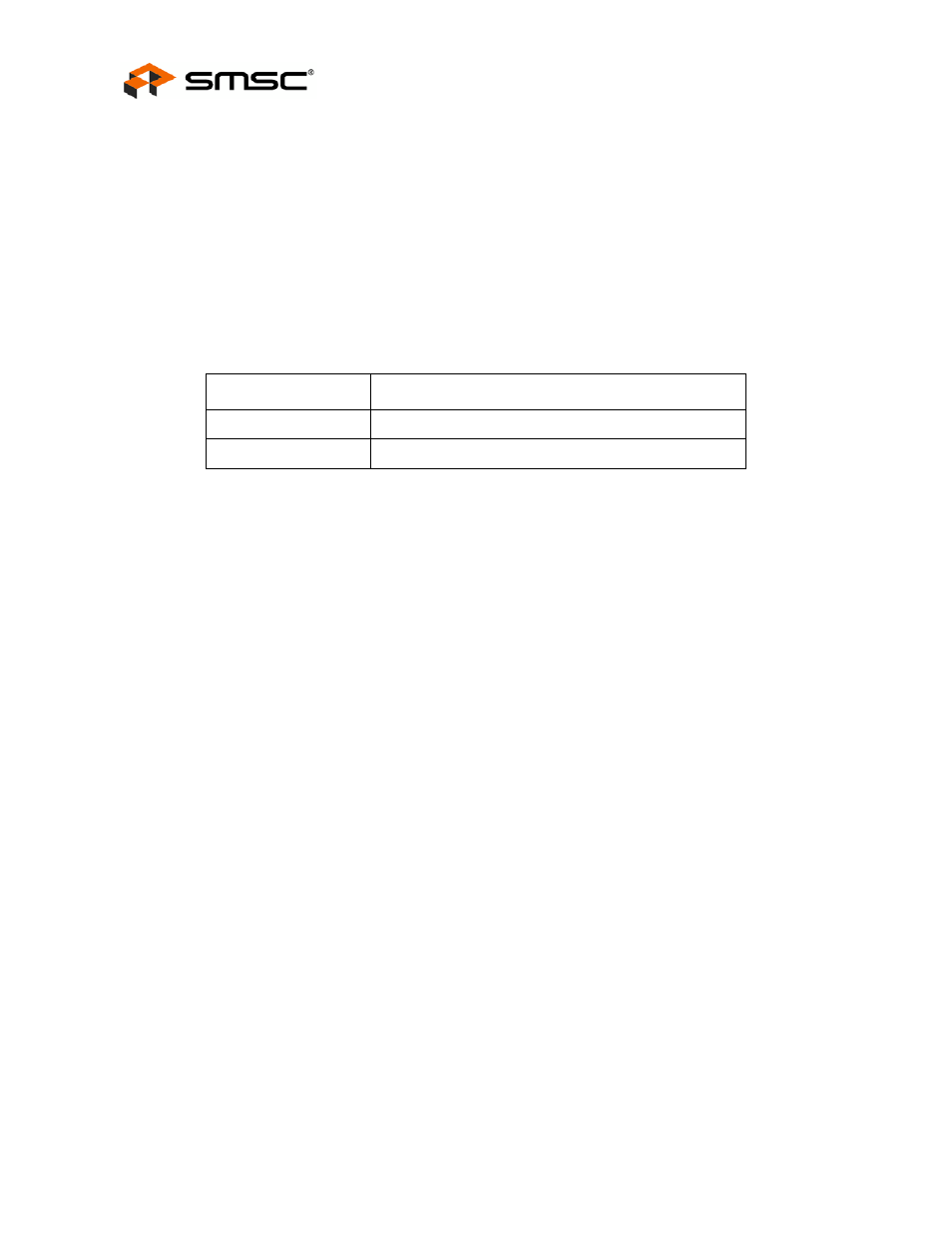

Table 4.2 REFCLK Modes

MODE

REF_CLK DESCRIPTION

REF_CLK In Mode

Sourced externally, driven on the XTAL1/CLKIN pin

REF_CLK Out Mode

Sourced by LAN8720/LAN8720i at the REFCLKO pin