Intel 8xC251TB User Manual

Page 14

8xC251Tx Hardware Description

8

The second serial I/O port interrupt is enabled by setting the ES1 bit in the IE1 register. The priority of the

second serial I/O port’s interrupt is set to one of four levels by programming the IPL1.0 and IPH1.0 bits in the

IPL1 and IPH1 registers, respectively. The second serial I/O port is last in the interrupt polling sequence (see

Chapter 6 of the 8xC251SA, 8xC251SB, 8xC251SP, 8xC251SQ Embedded Microcontroller User’s Manual

(272795) for details of the interrupt system). The second serial I/O port's Interrupt Service Routine Vector

Address is FF:0043H.

When the second serial I/O port is used, the alternate functions of RXD1 and TXD1 can no longer be used.

Specifically, the PCA can no longer be clocked by an external clock input since ECI now functions as RXD1.

The PCA can, however, be clocked by one of three other methods. They consist of two fixed frequencies

(fixed in relation to the Oscillator frequency); F

OSC

/12 and F

OSC

/4 and Timer 0 overflow.

The other consequence of using the second serial I/O port is Module 0 of the PCA can now be used only as a

16 bit Software Timer. The 16-bit Capture, High Speed Output and Pulse Width Modulation modes are no

longer available to Module 0 as these modes require the use of CEX0 (which, when the second serial I/O port

is in operation, functions as TXD1).

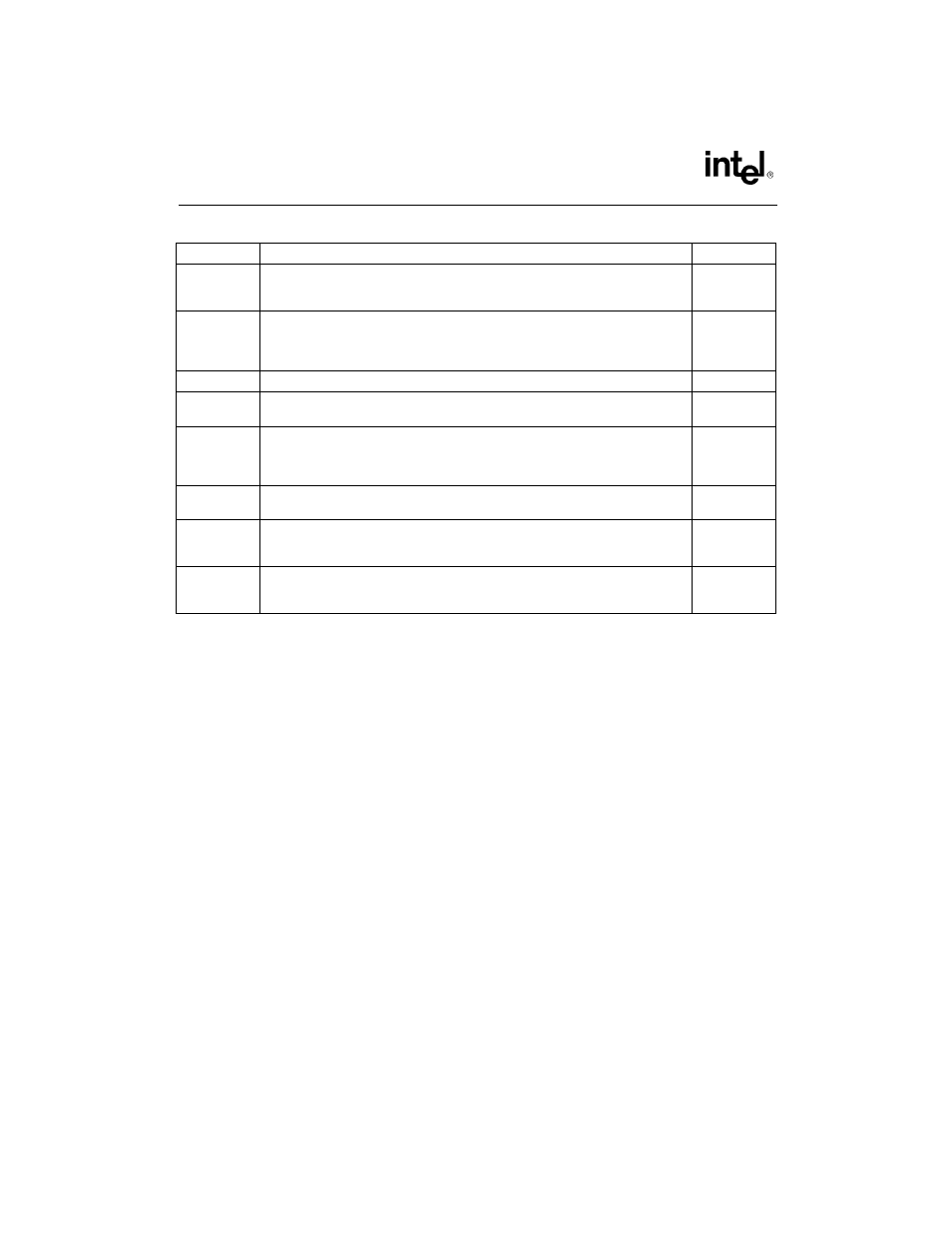

Table 5. Second Serial I/O Port Special Function Registers

Mnemonic

Description

Address

SBUF1

Serial Buffer 1. Two separate registers comprise the SBUF1 register. Writ-

ing to SBUF1 loads the transmit buffer; reading SBUF1 access the receive

buffer

9BH

SCON1

Serial Port Control 1. Selects the second serial I/O port operating mode.

SCON1 enables and disables the receiver, framing bit error detection, multi-

processor communication, automatic address recognition and the serial port

interrupt bits.

9AH

SADDR1

Serial Address 1. Defines the individual address for a slave device

AAH

SADEN1

Serial Address Enable 1. Specifies the mask byte that is used to define the

given address for a slave device

BAH

BGCON

Secondary Serial Port Control. Contains controls to the second serial port

including the double baud rate bit, read/write access to the SCON1.7 bit as

well as bits to control Timer1 or 2 overflow as the baud rate generator for

reception and transmission

8FH

IE1

Interrupt Enable Register 1. Contains the second serial I/O port interrupt

enable bit

B1H

IPL0

Interrupt Priority Low Control Register 1. IPL0, together with IPH0,

assigns the second serial I/O port interrupt level from 0 (lowest) to 3 (high-

est)

B2H

IPH0

Interrupt Priority High Control Register 1. IPH0, together with IPL0,

assigns the second serial I/O port interrupt level from 0 (lowest) to 3 (high-

est)

B3H