Intel 8xC251TB User Manual

Page 10

8xC251Tx Hardware Description

4

P3.0

P3.1

P3.2

P3.3

P3.4

P3.5

P3.6

P3.7

I/O

Port 3. This is an 8 bit, bidirectional I/O port with internal pullups

RXD

TXD

INT0#

INT1#

T0

T1

WR#

RD#/A16

PSEN#

O

Program Store Enable. Read signal output to external memory.

Asserted for the address range specified by the configuration byte

UCONFIG0, bits RD1:0.

RD#

O

Read. Read signal output to external memory. Asserted for the

address range specified by the configuration byte UCONFIG0, bits

RD1:0.

P3.7/A16

RST

I

Reset. Reset input to the chip. Holding this pin high for 64 oscillator

periods while the oscillator is running resets the device. The port pins

are driven to their reset conditions when a voltage greater than VIH1

is applied, whether or not the oscillator is running. This signal has a

Schmitt trigger input. Connecting the RST pin to V

CC

through a

capacitor provides power-on reset. Asserting RST when the chip is in

idle mode or powerdown mode returns the chip to normal operation.

RXD

I/O

Receive Serial Data. RXD send and receives data in serial I/O mode

0 and receives data in serial I/O modes 1, 2 and 3.

P3.0

RXD1

I/O

Receive Serial Data 1. RXD send and receives data in serial I/O

mode 0 and receives data in serial I/O modes 1, 2 and 3 for the sec-

ond serial I/O port.

P1.2/ECI

T1:0

I

Timer 1:0 External Clock Inputs. When Timer 1:0 operates as a

counter, a falling edge on the T1:0 pin increments the count.

P3.5:4

T2

I/O

Timer 2 Clock Input/Output. For Timer 2 capture mode, this signal

is the external clock input. For the clock-out mode, it is the timer 2

clock input.

P1.0

T2EX

I

Timer 2 External Input. In Timer 2 capture mode, a falling edge ini-

tiates a capture of Timer 2 registers. In auto-reload mode, a falling

edge causes the Timer 2 registers to be reloaded. In the up-down

counter mode, this signal determines the count direction:

•

1=up

•

0 = down.

P1.1

TXD

O

Transmit Serial Data. TXD outputs the shift clock in serial I/O mode

0 and transmits serial data in serial I/O modes 1, 2 and 3.

P3.1

TXD1

O

Transmit Serial Data 1. TXD outputs the shift clock in serial I/O

mode 0 and transmits serial data in serial I/O modes 1, 2 and 3 for the

second serial I/O port.

P1.3/CEX0

V

CC

PWR

Supply Voltage. Connect this pin to the +5 supply voltage.

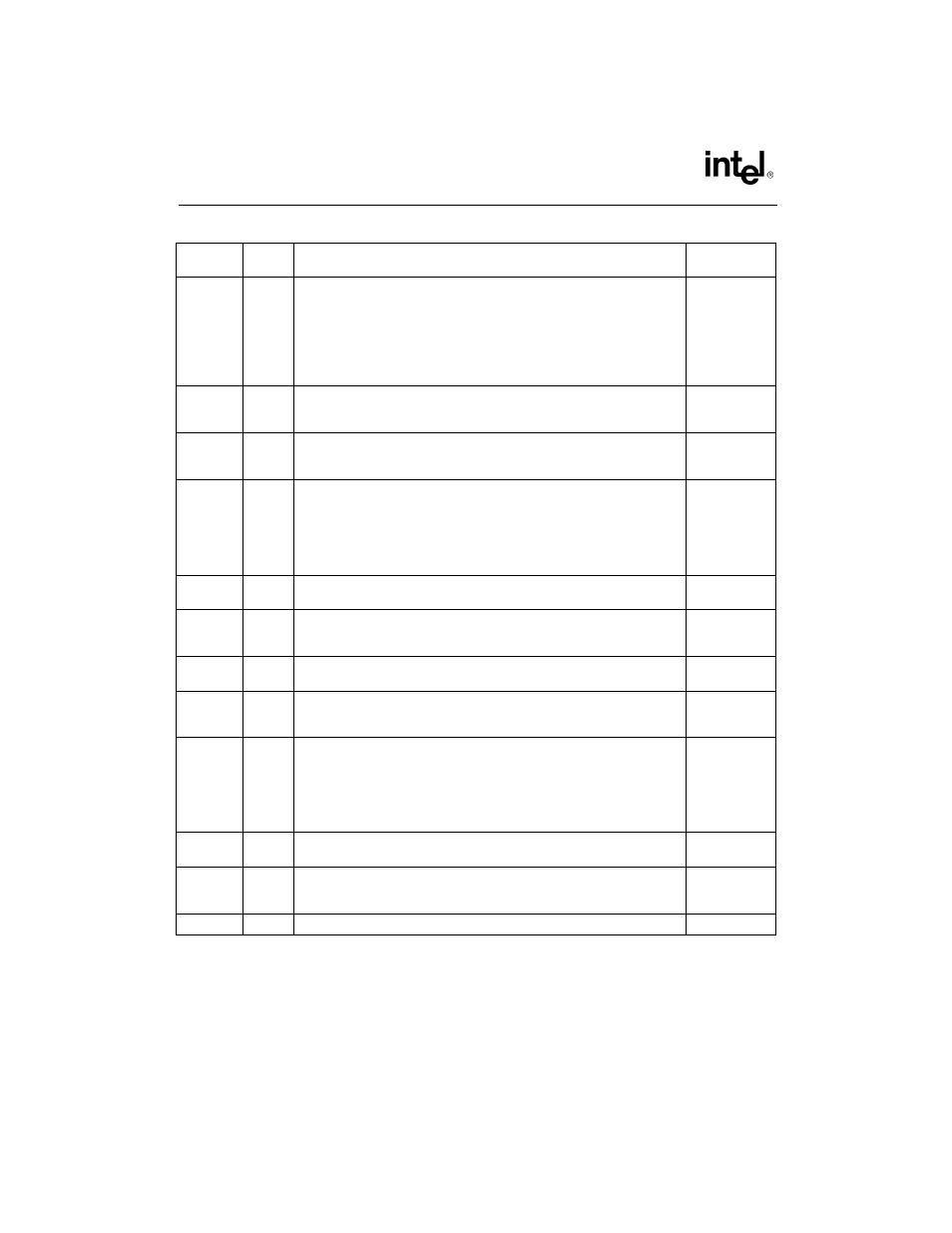

Table 2. 8xC251Tx Signal Descriptions (Sheet 2 of 3)

Signal

Name

Type

Description

Alternate

Function

* The descriptions of A15:8/P2.7:0 and AD7:0/P0.7:0 are for non page mode configuration. If configured in

page mode, Port 0 carries the lower address bits (A7:0) and Port 2 carries the upper address bits (A15:8)

and the data (D7:0)