System memory, Pci bus, Chapter 2. system board features – IBM 6288 User Manual

Page 12

Chapter 2. System board features

System memory

The system memory interface is controlled by the Intel 82810 chip set. PCI 100 synchronous dynamic

random access memory (SDRAM) is standard.

The maximum amount of system memory is 512 MB. For memory expansion, the system board provides

two dual inline memory module (DIMM) connectors. 100 MHz DIMMs in sizes of 32 MB, 64 MB, 128 MB,

and 256 MB are supported. The amount of memory preinstalled varies by model.

The following information applies to system memory:

SDRAM, nonparity, unbuffered, 3.3V memory is standard.

The maximum height of memory modules is 6.35 cm (2.5 in.).

Only PC 100 industry-standard, gold-contact DIMMs are supported.

The PC 300GL does not support error correcting code (ECC).

Auto-configure, auto-detect maximum system memory, using serial presence detect and configuration

interface (BIOS specific).

For information on the pin assignments for the memory module connectors, see “Memory connectors” on

page 25.

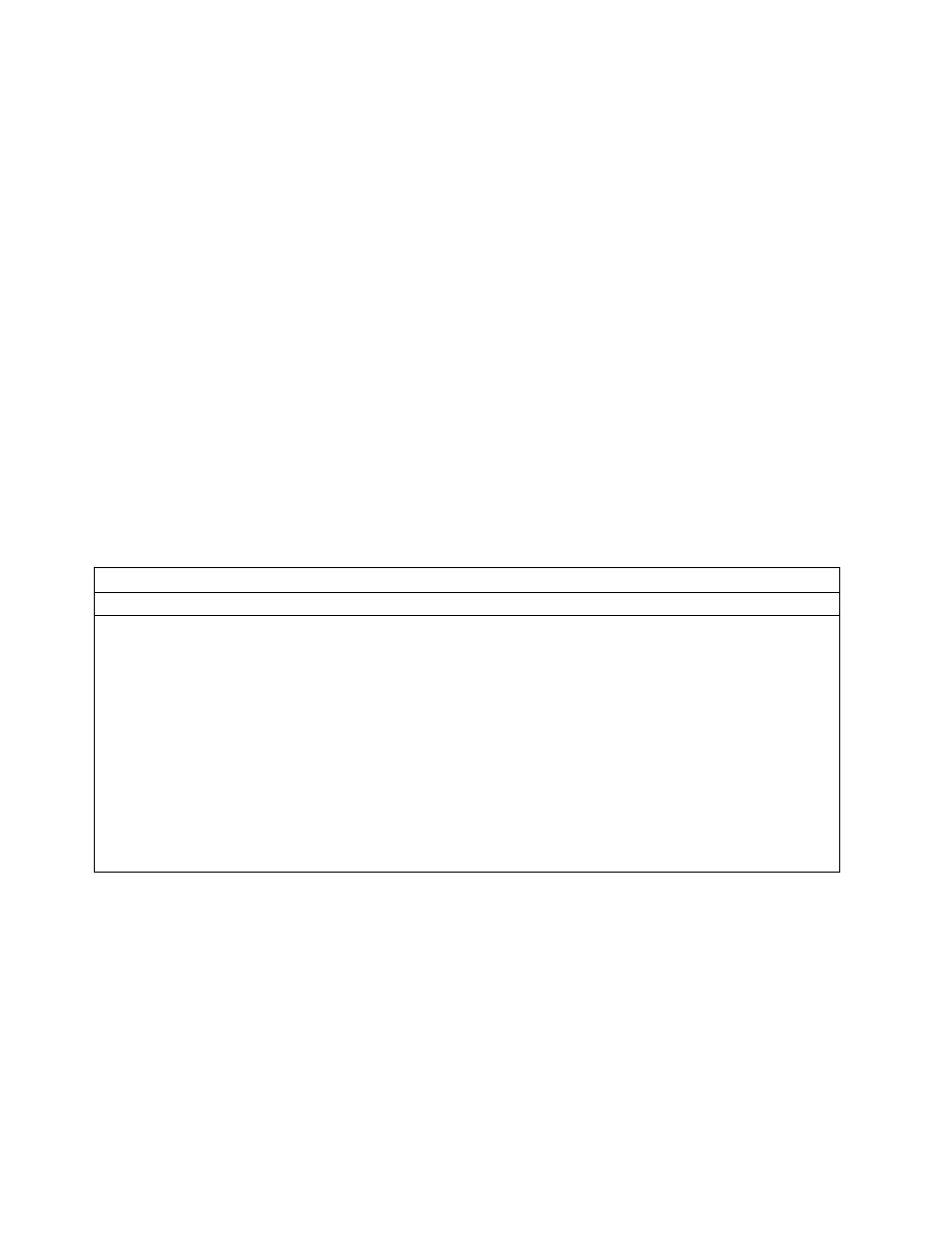

The following figure shows some possible configurations for the supported DIMMs.

Note: Values in the following table are represented in megabytes (MB).

Figure 1. Memory configurations

Total memory (MB)

DIMM 0

DIMM 1

32

32

0

64

32

32

64

64

0

96

64

32

128

64

64

128

128

0

160

128

32

192

128

64

256

128

128

384

256

128

512

256

256

PCI bus

The fully synchronous 33 MHz PCI bus originates in the Intel 82801 chip. Features of the PCI bus are:

Integrated arbiter with multitransaction PCI arbitration acceleration hooks

Zero-wait-state, microprocessor-to-PCI write interface for high performance graphics

Built-in PCI bus arbiter with support for up to five masters

Microprocessor-to-PCI memory write posting with 5-Dword-deep buffers

Converts back-to-back sequential microprocessor-to-PCI memory write to PCI burst write

PCI-to-DRAM posting 18 Dwords

PCI-to-DRAM up to 100+ MB/sec bandwidth

Multitransaction timer to support multiple short PCI transactions within one PCI ARB cycle

PCI 2.2/2.3 compliant

4

Technical Information Manual