Revision history – Intel 80960HD User Manual

Page 6

Contents

6

Datasheet

Revision History

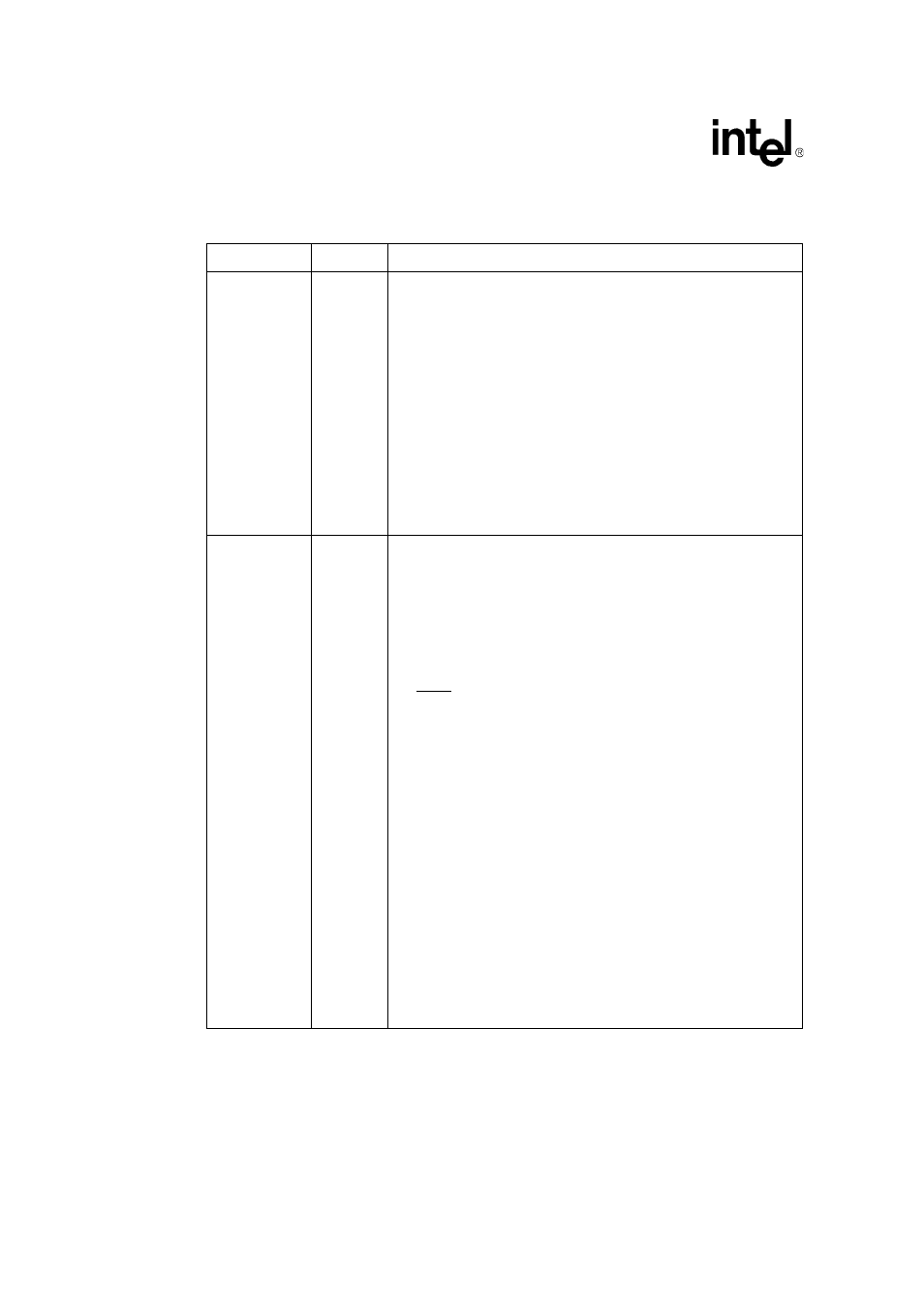

Date

Revision

History

September 2002

008

Formatted the datasheet in a new template.

In

“32-Bit Parallel Architecture” on page 1

:

•

Removed operating frequency of 16/32 (bus/core) from 80960HD.

•

Removed operating frequency of 20/60 (bus/core) from 80960HT.

In

Table 5 “80960HA/HD/HT Package Types and Speeds” on page 14

:

•

Removed core speed of 32 MHz and bus speed of 16 MHz, and order

number A80960HD32-S-L2GG from the 168L PGA package, 80960HD

device.

•

Removed core speed of 60 MHz and bus speed of 20 MHz, and order

number A80960HT60 from the 168L PGA package, 80960HT device.

•

Removed core speed of 32 MHz and bus speed of 16 MHz, and order

number FC80960HD32-S-L2GL from the 208L PQFP package,

80960HD device.

•

Removed core speed of 60 MHz and bus speed of 20 MHz, and order

number FC80960HT60-S-L2G2 from the 208L PQFP package,

80960HT device.

July 1998

007

In

“32-Bit Parallel Architecture” on page 1

:

•

Revised 1.2 Gbyte Internal Bandwidth (75 MHz) to 1.28 Gbyte Internal

Bandwidth (80 MHz).

In

Section 3.0, “Package Information” on page 14

:

•

Added paragraph two and

Table 5 “80960HA/HD/HT Package Types

and Speeds” on page 14

.

In

Table 7 “80960Hx Processor Family Pin Descriptions” on page 16

:

•

Corrected minor typeset and spacing errors.

•

BREQ; Revised description.

•

ONCE; last sentence, changed ‘low’ to ‘high’.

•

TDI and TMS; removed last sentence stating, “Pull this pin low when

not in use.”

In

Figure 2 “80960Hx 168-Pin PGA Pinout—View from Top (Pins Facing

Down)” on page 20

:

•

Added insert package marking diagram.

In

Figure 4 “80960Hx 208-Pin PQ4 Pinout” on page 26

:

•

Added insert package marking diagram.

In

Table 10 “80960Hx PQ4 Pinout—Signal Name Order” on page 27

:

•

Corrected TDO (‘O’ was zero) and revised alphabetical ordering.

In

Table 11 “80960Hx PQ4 Pinout—Pin Number Order” on page 29

:

•

Corrected TDO (‘O’ was zero) and revised alphabetical ordering.

In

Section 4.1, “Absolute Maximum Ratings” on page 37

:

•

Revised V

CC

to VCC5 for Voltage on Other Pins with respect to V

SS

.

In

Section 4.5, “VCCPLL Pin Requirements” on page 39

:

•

Added section.

In

Table 22 “80960Hx DC Characteristics” on page 40

:

•

Added footnote (1) to I

LO

notes column for TDO pin.

•

Added footnote (10) to C

IN

, C

OUT

and C

I/O

pin.