English frequency/voltage control – GIGABYTE 7VM333M-RZ User Manual

Page 29

- 29 -

BIOS Setup

English

Frequency/Voltage Control

Auto Detect PCI/DIMM Clk

Disabled

Disable this function.

Enabled

Auto detect PCI/DIMM c lock. (Default v alue)

Spread S pectrum

Disabled

Disable this function.

Enabled

Enable clock s pread spectrum. (Default v alue)

CPU Host Clock Control

Note: If sy stem hangs up before enter CMOS setup utility , w ait for 20 sec for tim es out reboot.

When time out occur, sy s tem w ill reset and run at CPU default Host cloc k at nex t boot.

Disabled

Disable CPU Host Clock C ontrol. (Default v alue)

Enabled

Enable CPU Host Clock Control.

CPU Clock

100

Set C PU Host C lock to 100MHz~132MHz.

133

Set C PU Host C lock to 133MHz~165MHz.

166

Set CPU Host Clock to 166MHz~199MHz.

DRAM Clock (MHz)

Wrong frequency may make sy stem can't boot, c lear CMOS to ov ercome w rong frequency issue.

By SPD

Set m emory frequency by DRAM SPD data. (Default v alue)

133-DDR266

If y ou use DDR266 DRAM m odule, please set at "133-DDR 266".

166-DDR333

If y ou use DDR333 DRAM m odule, please set at "166-DDR 333".

AGP Ov erVoltage Control

Increase AGP v oltage may get stable for ov er-clock. But it may damage to AGP card w hen enable

this feature.

Auto

Supply v oltage as AGP required. (Default v alue)

+0.1V

Increase AGP v oltage +0.1V.

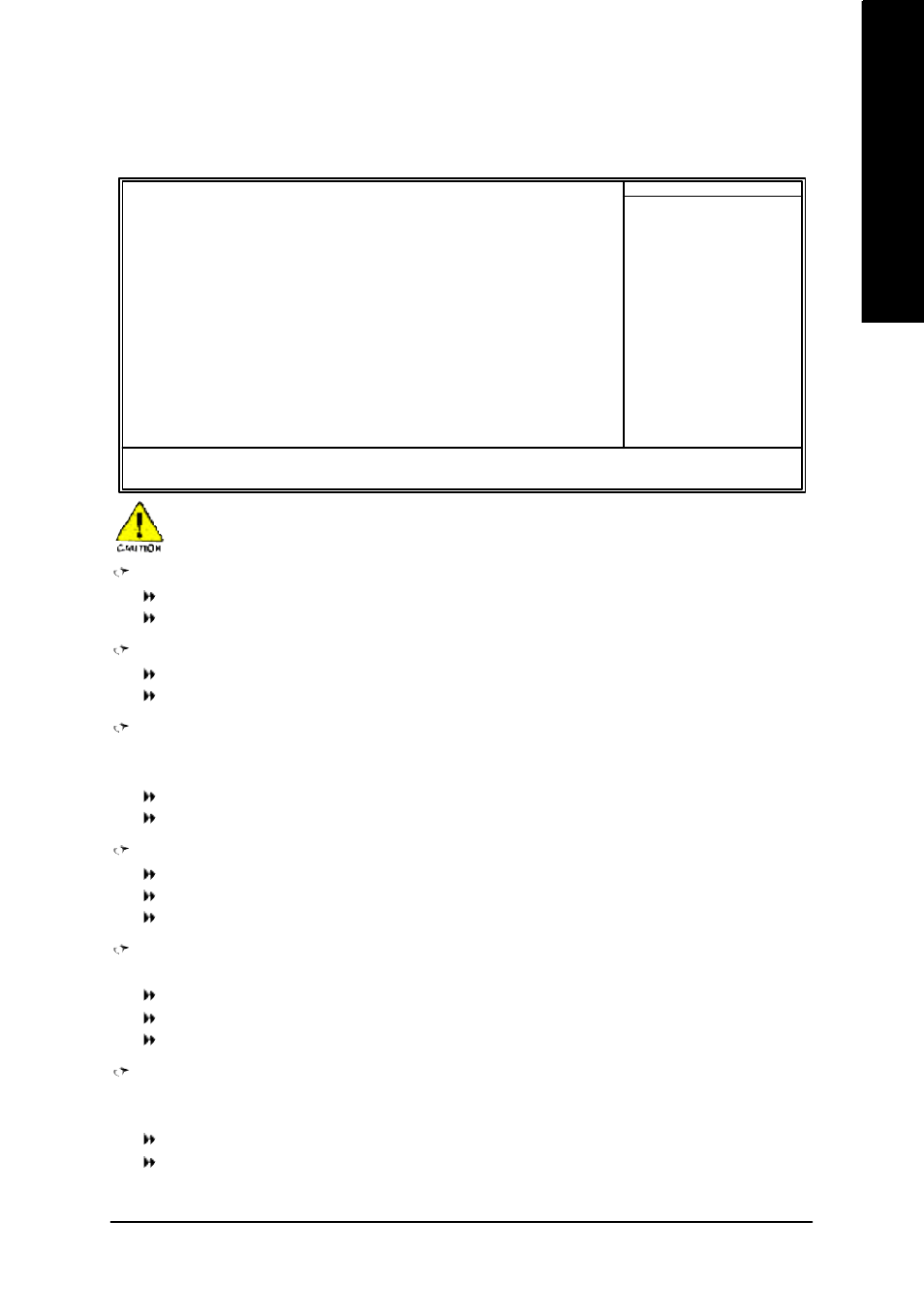

CMOS Setup Ut ility-Co pyright (C) 1984 -2004 Aw ard Soft ware

Frequ ency/Vol tage Con trol

Auto Detect PCI/DIMM Clk

[Enab led]

Spre ad Spec turm

[Enab led]

CPU Host Cl ock Con trol

[Disa bled]

x CPU C lock

133 MHz

DRAM Clock( MHz)

[By SPD]

AGP OverVolt age Con trol

[Au to]

DIMM OverVol tage Con trol

[Au to]

higf: M ove

Enter: Select

+/-/ PU/PD: V alue

F10: Save

ESC: Exit

F1: General Help

F5: P revious V alues

F6: Fa il-Save De fault

F7: Optimiz ed Defa ults

Item Help

Menu L evel

}

Incorrect using these features may cause y our sy stem broken. For pow er End-User use only !