FUJITSU MHT2060BH User Manual

Page 144

Interface

5-70 C141-E203-01EN

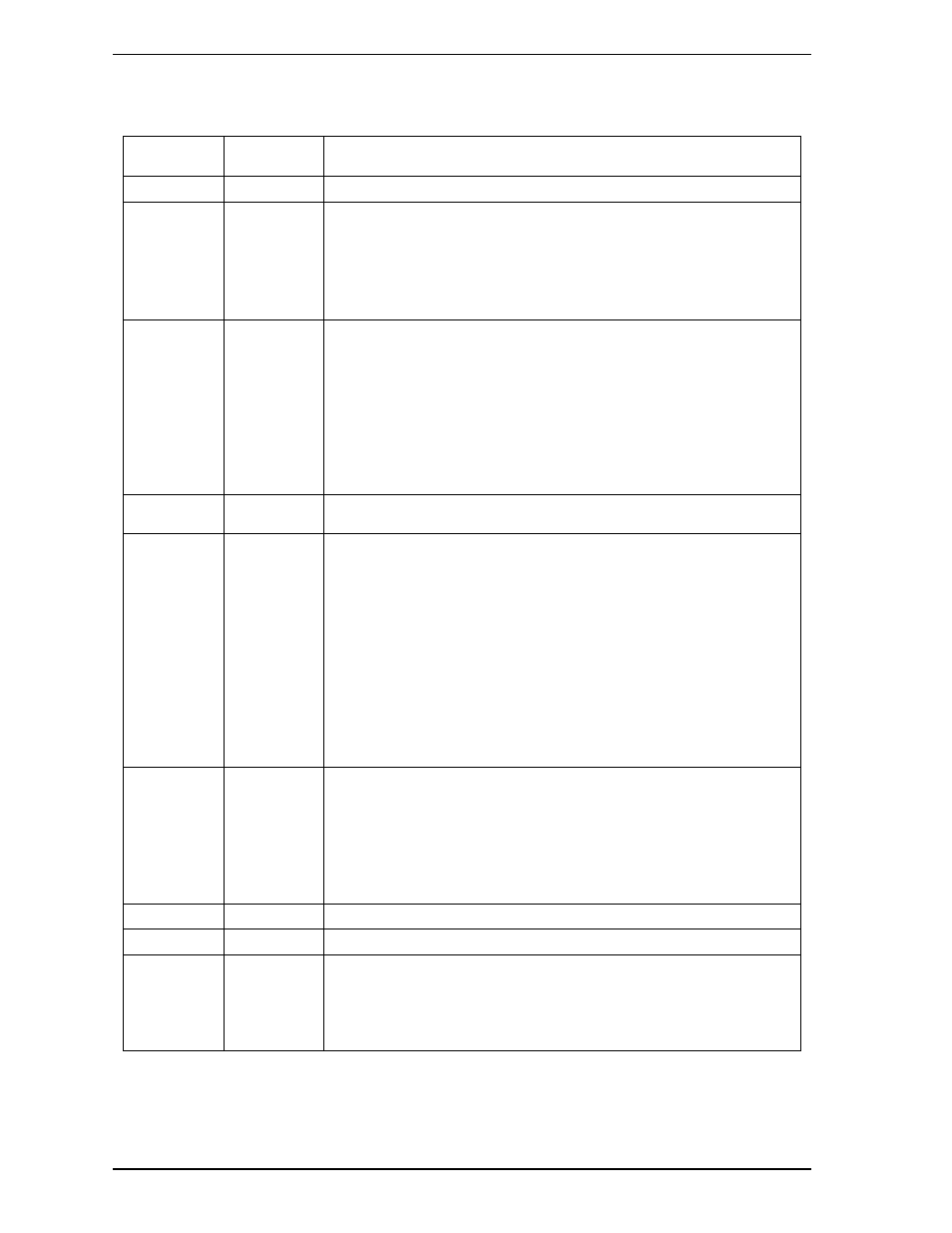

Table 5.23 DEVICE CONFIGURATION IDENTIFY data structure

Word Value

Content

0

X'0001'

Data structure revision

1

X'0007'

Multiword DMA modes supported

Reflected in IDENTIFY information "WORD63".

Bit 15-3:

Reserved

Bit 2:

1 = Multiword DMA mode 2 and below are supported

Bit 1:

1 = Multiword DMA mode 1 and below are supported

Bit 0:

1 = Multiword DMA mode 0 is supported

2

X'003F'

Ultra DMA modes supported

Reflected in IDENTIFY information "WORD88".

Bit 15-6:

Reserved

Bit 5:

1 = Ultra DMA mode 5 and below are supported

Bit 4:

1 = Ultra DMA mode 4 and below are supported

Bit 3:

1 = Ultra DMA mode 3 and below are supported

Bit 2:

1 = Ultra DMA mode 2 and below are supported

Bit 1:

1 = Ultra DMA mode 1 and below are supported

Bit 0:

1 = Ultra DMA mode 0 is supported

3 to 6

-

Maximum LBA address Reflected in IDENTIFY information

"WORD60-61". (WORD100-103) *

7 X'00CF'

(X'01CF') *

Command set/feature set supported

Reflected in IDENTIFY information "WORD82-87".

Bit 15-9:

Reserved

Bit 8:

1 = 48-bit Addressing feature set supported

Bit 7:

1 = Host Protected Area feature set supported

Bit 6:

1 = Automatic acoustic management supported

Bit 5:

1 = READ/WRITE DMA QUEUED commands supported

Bit 4:

1 = Power-up in Standby feature set supported

Bit 3:

1 = Security feature set supported

Bit 2:

1 = SMART error log supported

Bit 1:

1 = SMART self-test supported

Bit 0:

1 = SMART feature set supported

8

X ' 0005 '

Serial-ATA command set/function

→

Reflected in IDENTIFY information ”Word 76 to 79.

Bit15-4: Reserved

Bit3:

1 = Asynchronous Notification supported

Bit2:

1 = Interface power management supported

Bit1:

1 = Non-zero buffer offsets in DMA Setup FIS supported

Bit0:

1 = Native command queuing supported

9

X ' 0000 '

Reserved for Serial-ATA

10 to 254

X'0000'

Reserved

255

X'xxA5'

Bit 15-8:

Check sum code (This is obtained by calculating the sum of all

upper bytes and lower bytes in WORD 0 to 256 and the byte

consisting of bits 7 to 0 in WORD 255, and then calculating the

two's complement of the lowest byte of that sum.)

Bit 7 - 0: