Clock register d 0x1d, Clock register e 0x1e, Clock register f 0x1f – Sundance SMT942 User Manual

Page 22

User Manual SMT942

Page 22 of 55

Last Edited: 23/08/2011 17:25:00

0

‘0’

Normal mode of operation

1

‘1’

FB Divider can be started with external REF_SEL (pin)

Setting

Bit 9

Description DET_START_BYPASS

0

‘0’

Normal mode of operation

1

‘1’

FB Divider can be started with external NRESET (pin)

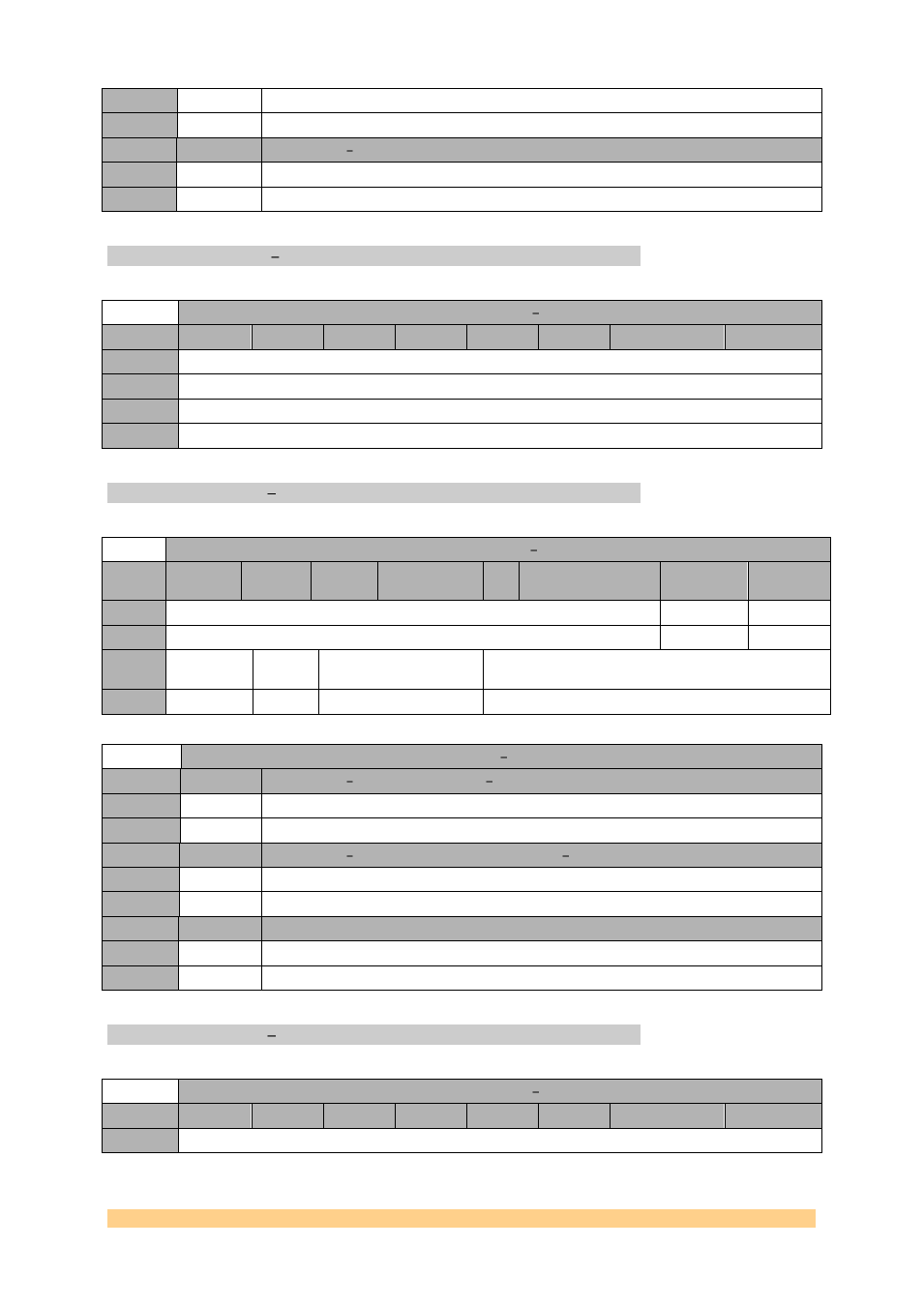

CLOCK Register D 0x1D.

Clock Register D 0x1D

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

Reserved

Default

‘01101000’

0

Reserved

Default

‘00000000’

CLOCK Register E 0x1E.

Clock Register E 0x1E

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit

3

Bit 2

Bit 1

Bit 0

1

Reserved

ADLOCK

LOCK_C[1]

Default

‘000000’

‘0’

‘0’

0

LOCK_C[0]

Reserve

d

LOCK_WINDOW

Reserved

Default

‘0’

‘0’

‘00’

‘0111’

Reset Register E 0x1E

Setting

Bit 5:4

Description Lock detect window LOCK_WINDOW

0

‘0’

1

‘1’

Setting

Bit 8:7

Description Number of coherent lock events LOCK_C

0

‘0’

1

‘1’

Setting

Bit 9

Description ADLOCK

0

‘0’

Digital PLL Lock

1

‘1’

Analog PLL Lock

CLOCK Register F 0x1F.

Clock Register F 0x1F

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

Reserved