Reset status register – IBM BDM-610000049 User Manual

Page 87

BDM-610000049

Rev G

Chapter 4: Using the cpuModule

77

Reset Status Register

The cpuModule has several different signals on board which can cause a system reset. If a reset occurs, the reset

status register can be used to see which reset or resets have been asserted on the cpuModule.

The user has the ability to see which resets have been asserted. Resets can also be cleared.

•

Examine Resets

: Reading from I/O port 0x457 will indicate if a reset has been asserted. If a 1 is read, the

corresponding reset has been asserted. If a 0 is read from the bit, the reset has not been asserted

•

Clear Reset

: Each reset can be cleared by writing a 1 to the selected bit of I/O port 0x457.

Main Power (+5V)

1 = reset asserted

0 = no reset

Non-Standby Power

1 = reset asserted

0 = no reset

Standby Power

1 = reset asserted

0 = no reset

PCI Reset

1 = reset asserted

0 = no reset

CPU Core Power

1 = reset asserted

0 = no reset

Memory Power

1 = reset asserted

0 = no reset

Reserved

Utility Reset

1 = reset asserted

0 = no reset

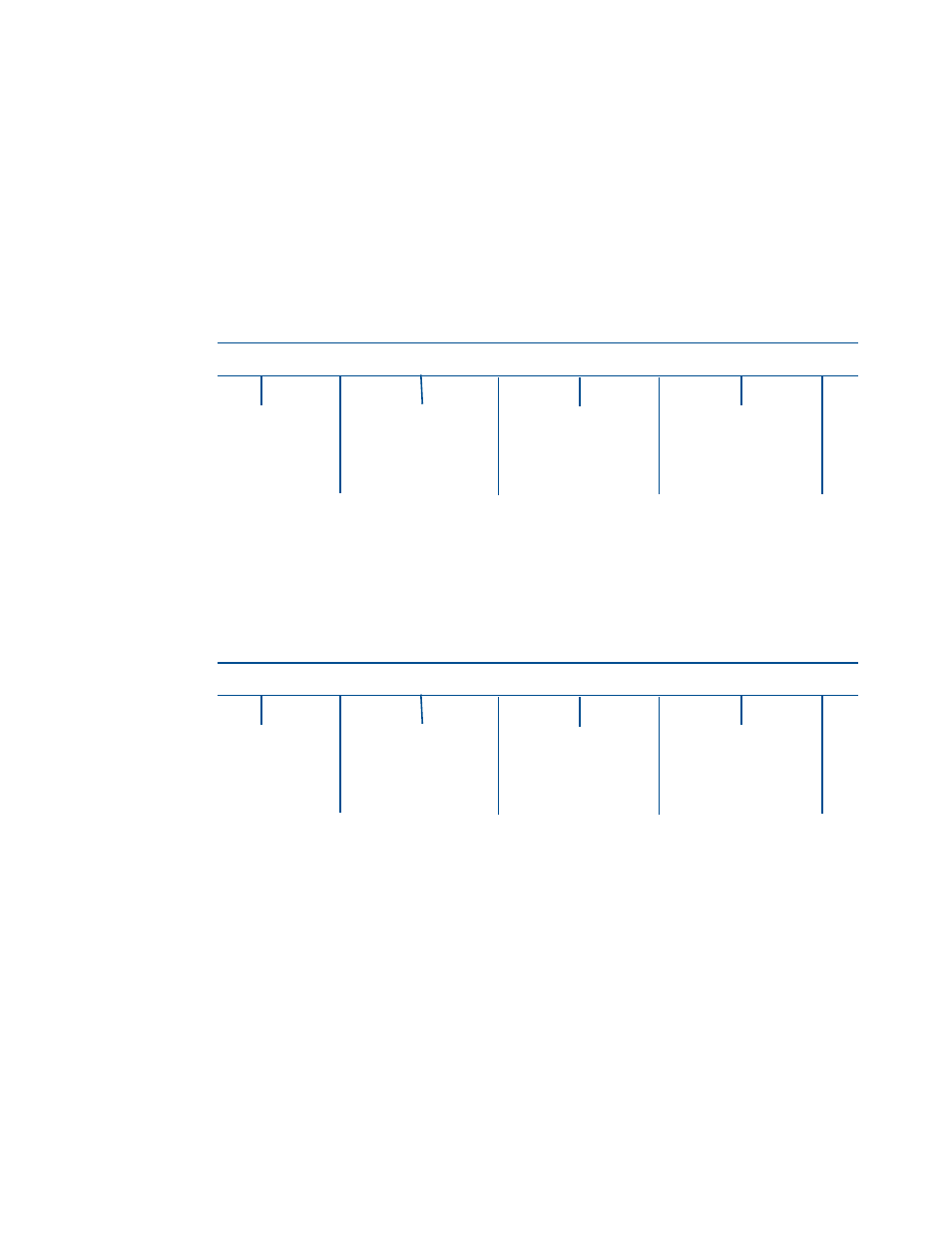

Table 57

Reset Status I/O Address 457h - Read Access

D7

D6

D5

D4

D3

D2

D1

D0

Main Power (+5V)

1 = clear reset

Non-Standby Power

1 = clear reset

Standby Power

1 = clear reset

PCI Reset

1 = clear reset

CPU Core Power

1 = clear reset

Memory Power

1 = clear reset

Reserved

Utility Reset

1 = clear reset

Table 58

Reset Status I/O Address 457h - Write Access

D7

D6

D5

D4

D3

D2

D1

D0