Chapter 3, Board layout – Lanner LEC-6020 User Manual

Page 18

18

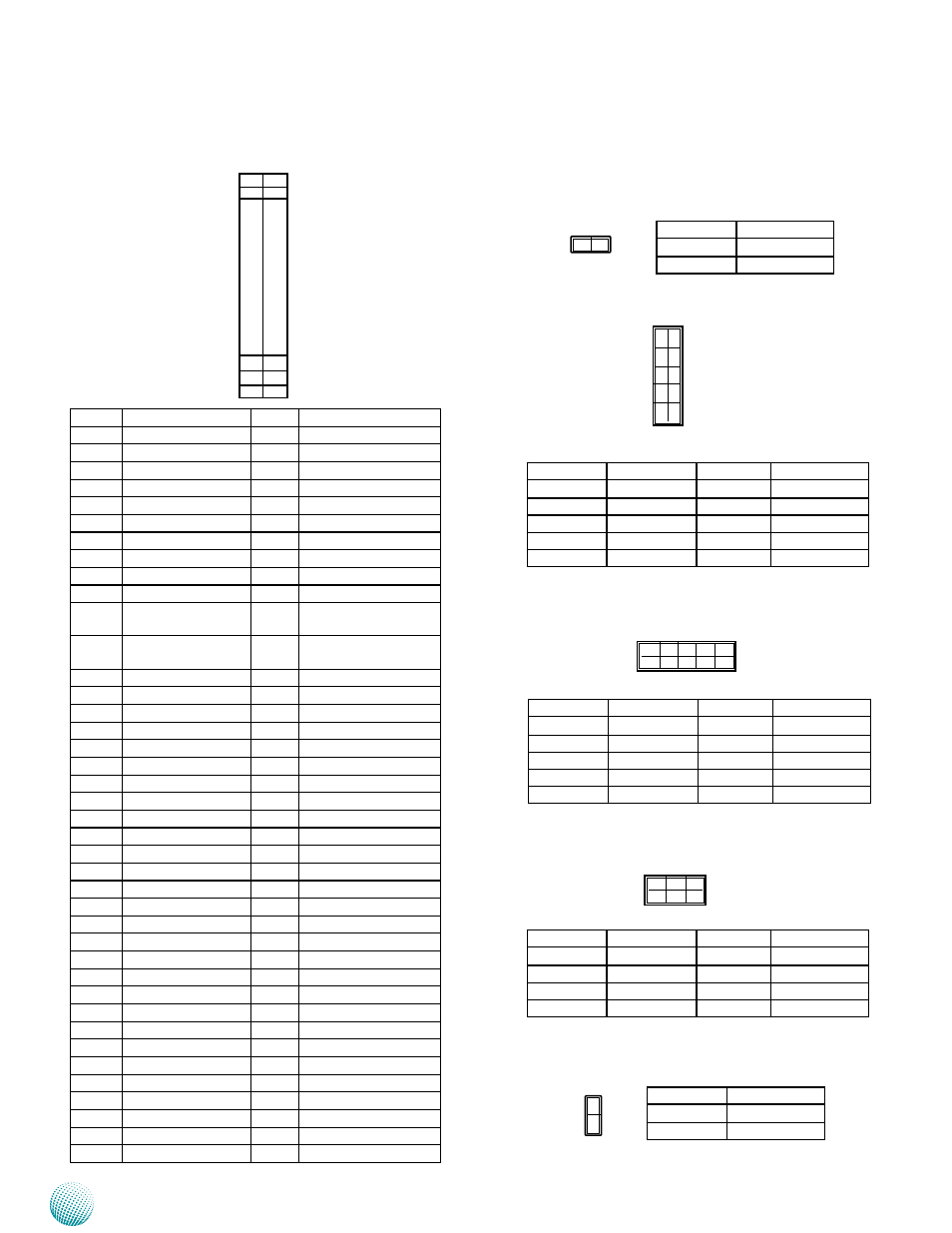

Board Layout

Chapter 3

Embedded and Industrial Computing

Clear CMOS jumper (CLR1): It is for clearing the CMOS

memory.

Board to Board Power Connector (JP1)

Serial Port Connector (COM1)

Keyboard and Mouse Connector (KBMS1)

Power Button (PWR1)

Board to Board Connector (J3)

PIN

Description

PIN

Description

1

GND

2

GND

3

USB_P2_DN

4

PCIE_RX2_DN

5

USB_P2_DP

6

PCIE_RX2_DP

7

GND

8

GND

9

USB_P3_DN

10

PCIE_TX2_C_DN

11

USB_P3_DP

12

PCIE_TX2_C_DP

13

GND

14

GND

15

USB_P6_DN

16

PCIE_RX3_DN

17

USB_P6_DP

18

PCIE_RX3_DP

19

GND

20

GND

21 SMB_CLK_RESU

ME_IO

22

PCIE_TX3_C_DN

23 SMB_DATA_RES

UME_IO

24

PCIE_TX3_C_DP

25

GND

26

GND

27

USB_OC_N23

28 CLK_MULTI_IO_ DN

29

PM_CLKRUN_N

30 CLK_MULTI_IO_ DP

31

GND

32

GND

33

CLK_33M_TPM

34 CLK_MINIPCIE_ DN

35

L_AD3

36

CLK_MINIPCIE_ DP

37

L_AD2

38

GND

39

L_AD1

40

GND

41

L_AD0

42

PLTRST_BUF2_N

43

L_FRAME_N

44

WAKE_N

45

SER_IRQ

46

SIO_GP00

47

P5VS

48

SIO_GP01

49

P5VS

50

COM2_RTS#

51

P5VS

52

COM2_TXD#

53

P5VS

54

COM2_CTS#

55

P5VS

56

COM2_RXD#

57

WDTO_OUT#

58

COM3_RTS#

59

P3V3S

60

COM3_TXD#

61

P3V3S

62

COM3_CTS#

63

P3V3S

64

COM3_RXD#

65

P3V3S

66

COM4_RTS#

67

P3V3S

68

COM4_TXD#

69

P3V3S

70

COM4_CTS#

71

SIO_GP54

72

COM4_RXD#

73

P1V5

74

COM5_RTS#

75

P1V5

76

COM5_TXD#

77

P1V5

78

COM5_CTS#

79

P1V5

80

COM5_RXD#

1

79

2

80

Pin No.

Pin Name

1-2

Clear CMOS

NC (Default)

Normal

1 2

Pin No.

Pin Name

Pin No.

Pin Name

1

NC

2

P12V

3

GND

4

P12V

5

GND

6

P12V

7

GND

8

P12V

9

GND

10

P12V

9

1

10

2

Pin No.

Pin Name

Pin No.

Pin Name

1

SP1_DCD#

2

SP1_DSR#

3

SP1_RXD

4

SP1_RTS#

5

SP1_TXD

6

SP1_CTS#

7

SP1_DTR#

8

SP1_RI#

9

CAGND

1

2

9

10

8

7

2

1

Pin No.

Pin Name

Pin No.

Pin Name

1

P5VS

2

MSCLK

3

MSDAT

4

5

KBDAT

6

7

GND

8

KBCLK

1

2

Pin No.

Pin Name

1-2

Power On/Off

NC (Default)

Normal