Or tis_reset – Sundance SMT338 User Manual

Page 12

Version 1.5

Page 12 of 19

SMT338 User Manual

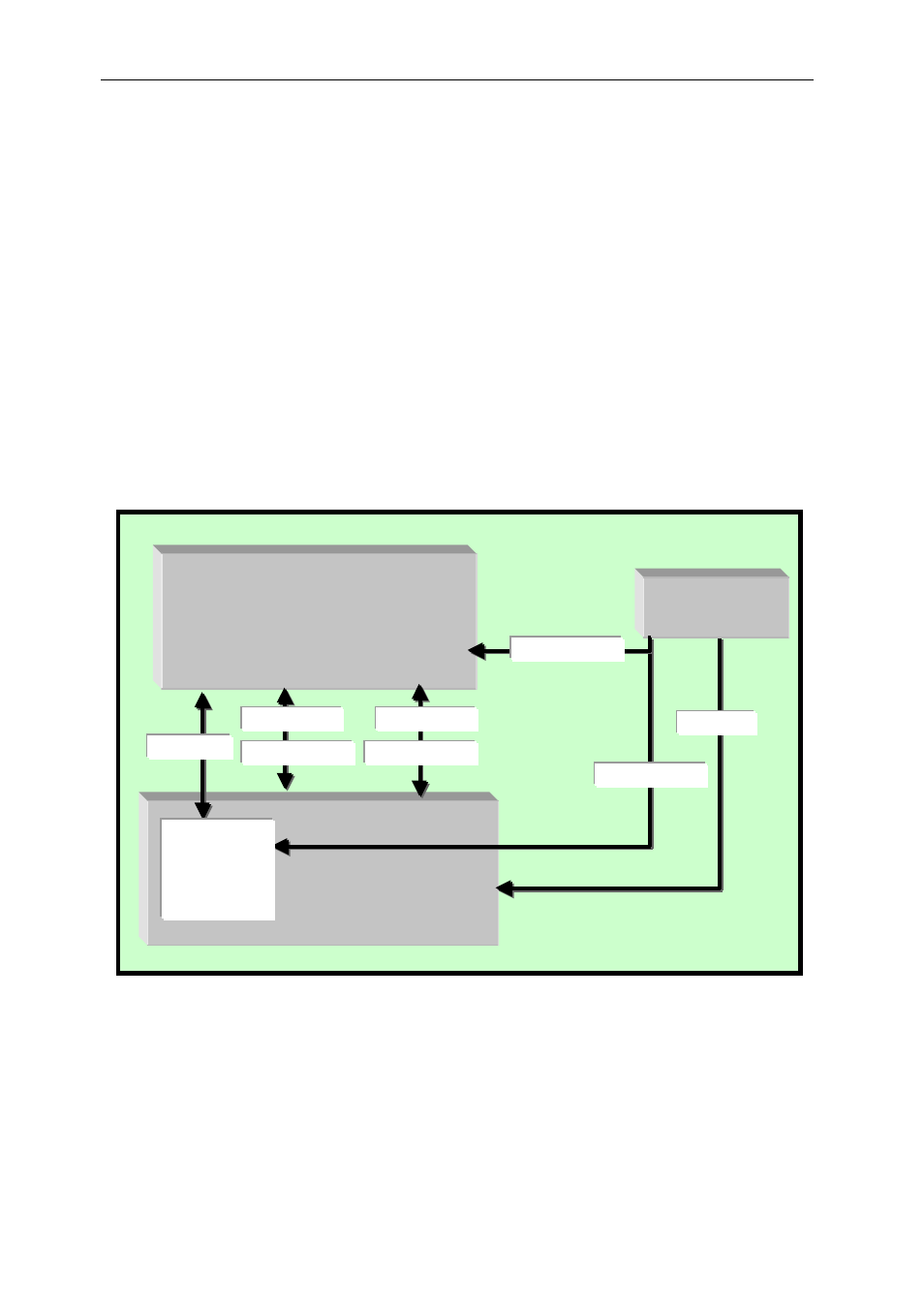

• If the design inside the FPGA instantiates Comm-Port 3: it must be kept reset

while the bitstream finishes to be downloaded. To do so, use the

FPGARESET pin as a global reset for the Comm-Port interface in particular

and for the whole design in general. FPGARESET is a bi-directional active low

signal. The CPLD asserts FPGARESET low until it receives the end-of-

bitstream word BCBCBC00 defining the end of the configuration process and

enters into an IDLE State waiting for an interrupt (general TISRESET from the

PCI or FPGARESET coming from the FPGA this time).

• If the design inside the FPGA doesn’t instantiate Comm-Port 3: The CPLD

asserts FPGARESET low until it receives the end-of-bitstream word

0xBCBCBC00 defining the end of the configuration process and enters into an

IDLE State waiting for an interrupt (general TISRESET from the PCI or

FPGARESET from the FPGA). Meanwhile, the FPGA design can start if it

doesn’t use FPGARESET as a global reset. (but a good practice is to use

FPGA RESET as a global reset).

Figure 5: Global Reset routing. Use of FPGARESET as a global reset for designs.

FPGA

XCVxxxxxBG352

Configuration Logic CPLD

Config Control

Top Primary

Connector

Com-Port 3

Com-Port 3 Ctrl

Com-Port 3 Data

Config D[7:0]

TIS_RESET

FPGARESET

TIS_RESET

FPGARESET

Logic

OR

TIS_RESET