Host memory, Channel handler, Figure 8 - layout of the sram memory – Sundance SMT6025 v.2.9 User Manual

Page 24

Version 2.9

Page 24 of 45

SMT6025 User Manual

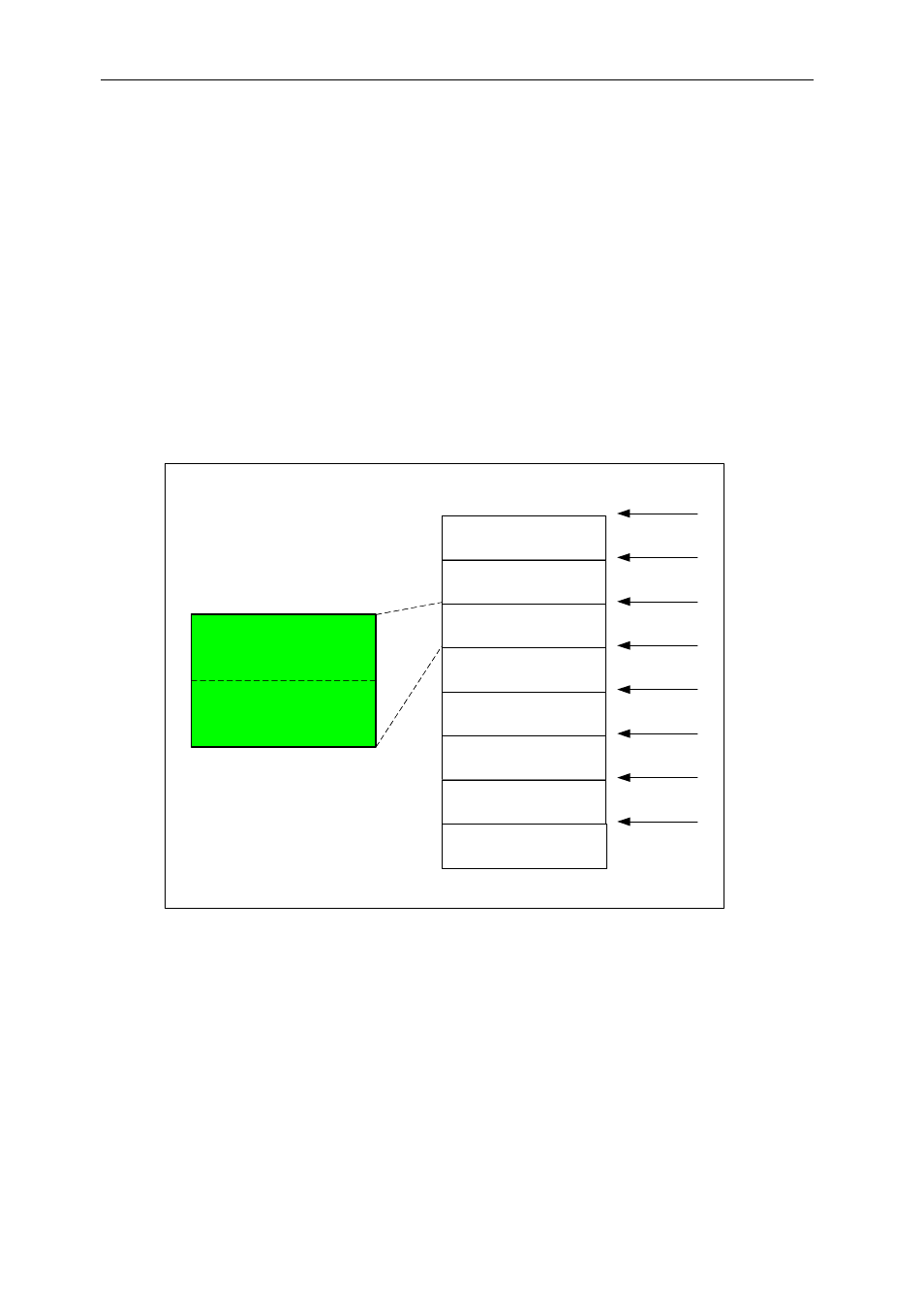

15.4.2 Host memory

The host can lock down a region of its memory and make this available

to the DSP over the PCI bus. The host memory needs to be locked

down in order for the DSP to safely gain access this memory. The host

places Information necessary for the DSP to access this memory in a

section of the carrier board’s SRAM reserved for this purpose. This

information is known as a memory descriptor list (MDL), and each MDL

can describe an area of host memory up to 16MB in size. There is one

MDL for each HSC.

The host operating system will not page to disk any locked down

memory, and will ensure that the memory remains at a fixed physical

location.

Channel 0 MDL

Channel 1 MDL

Channel 2 MDL

Channel 3 MDL

Channel 4 MDL

Channel 5 MDL

Channel 6 MDL

Channel 7 MDL

0x00000

0x20000

0x40000

0x60000

0x80000

0xA0000

0xC0000

0xE0000

Byte offset

64KB Area for

MDL

64KB SRAM

argument area

SRAM memory

Figure 8 - Layout of the SRAM memory

15.5 Channel handler

A channel handler is software that runs on the host and performs actions on

behalf of the DSP. Figure 9 describes the operation of a handler.

User Manual (QCF42); Version 2.9, 22/02/02; © Sundance Multiprocessor Technology Ltd. 2002