Hardware overview, Comport, The cpld – Sundance SMT6025 v.2.9 User Manual

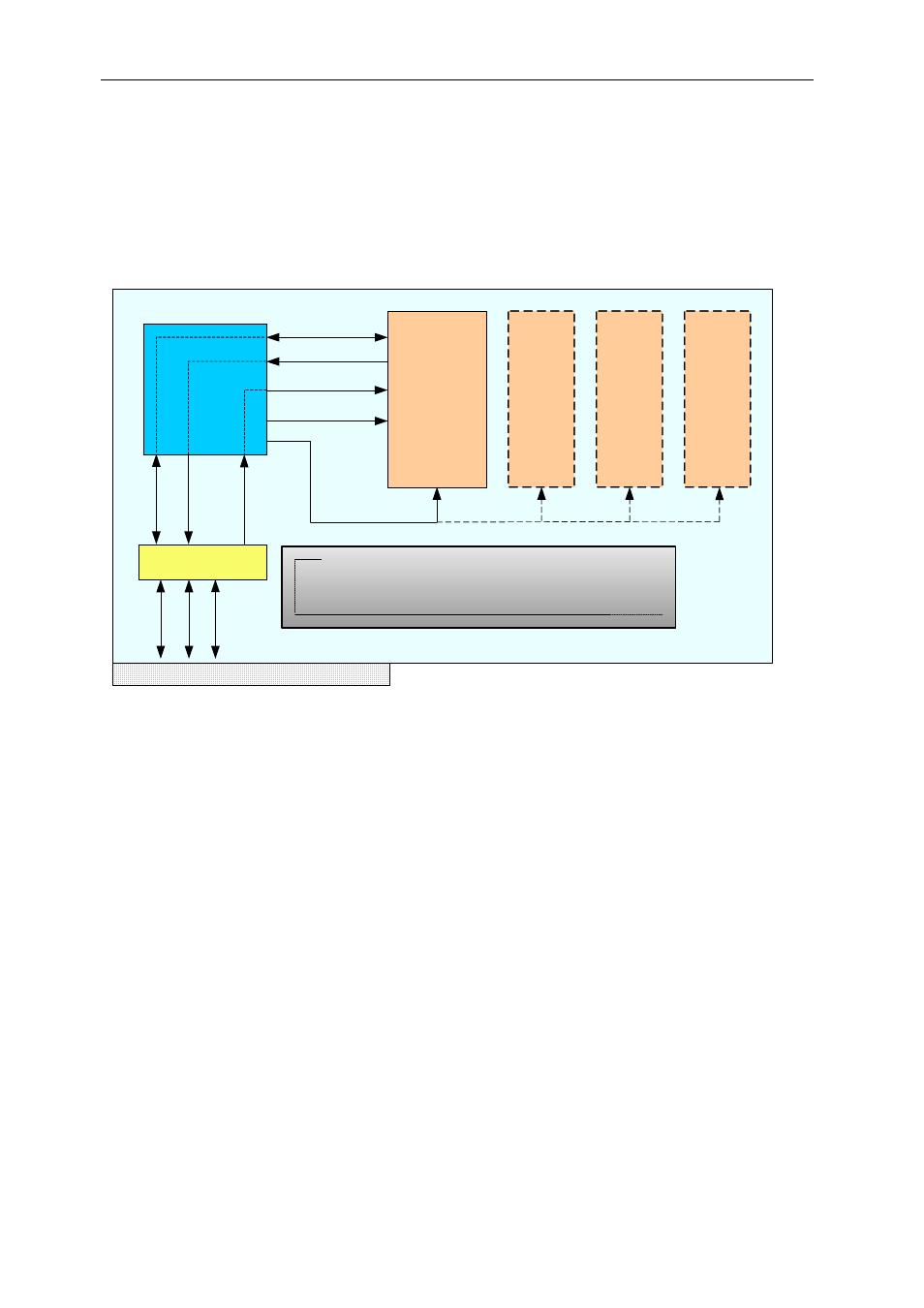

Page 10: Figure 5 - overview of the hardware, 8 hardware overview

Version 2.9

Page 10 of 45

SMT6025 User Manual

8 Hardware

overview

You need to be aware of the assumptions the SMT6025 makes about hardware

resources. This section provides a basic overview of the main hardware features

and shows how the SMT6025 interacts with them. The carrier board’s User

Manual contains a more detailed description of the hardware.

PCI Bridge (BAR 0)

TIM site 1

(Boot loader

supports

loading binary

files from

comport)

TIM site

2

TIM site

3

TIM site

4

Comport

IIOF0

IIOF1

IIOF2

L

IN

T

(

IIO

F2

)

Co

m

p

o

rt

In

tD

C

o

m

por

t

In

tA

CPLD (BAR 1)

The Bridge chip forms the link between the host and the DSP.

The mailbox registers are contained in the bridge chip.

PCI

Reset

Figure 5 - Overview of the hardware.

The figure above illustrates the main hardware concepts of a typical Sundance

carrier board.

8.1 Comport

A comport is a general mechanism for transferring data between components of

your system. Most TIM modules have several comports that can connect to

other TIMs or the host. These connections are usually made with FMS cables,

but some boards have built-in connections that can be controlled by carrier

board registers; the User Manual for your board will describe these registers in

detail. The standard board configuration will connect comport 3 on TIM site 1 to

the host.

8.2 The CPLD

The CPLD is used to configure the carrier board. It allows you to select the

direction of signals on the carrier board, select interrupt sources and set the

routing of the IIOF lines. The CPLD registers are mapped in BAR1 of the PCI

User Manual (QCF42); Version 2.9, 22/02/02; © Sundance Multiprocessor Technology Ltd. 2002