State of the iiof lines, The pci bridge chip – Sundance SMT6025 v.2.9 User Manual

Page 11

Version 2.9

Page 11 of 45

SMT6025 User Manual

bridge chip. The carrier board’s User Manual gives more information about the

CPLD.

8.3 State of the IIOF lines

The LINT (local interrupt) line on the global bus side of the PCI bridge chip can

be switched to any of the IIOF lines that go to the DSP.

The initial configurations of the IIOF lines are as follows:

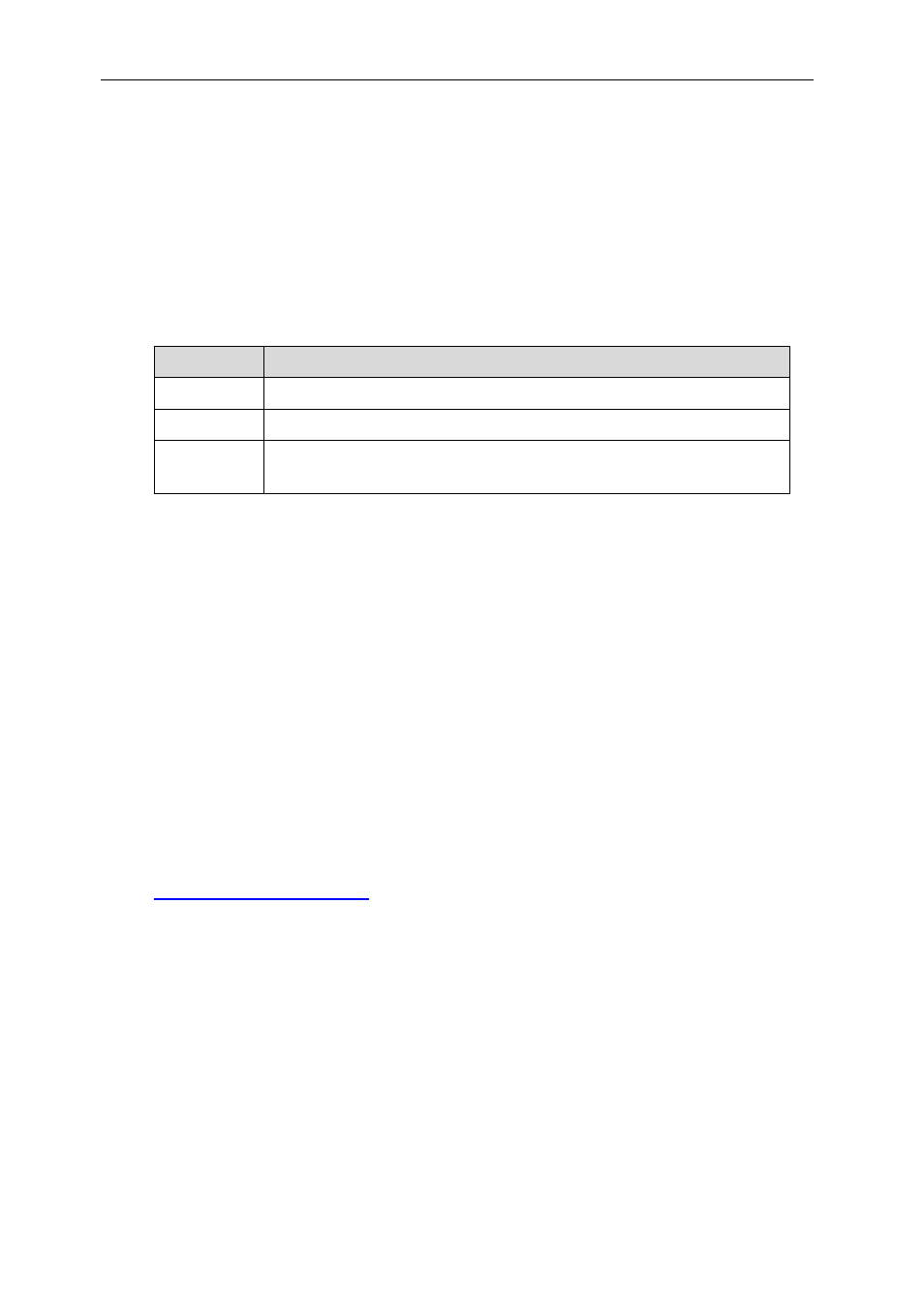

Line

Use or direction

IIOF0

Host to DSP

IIOF1

DSP to Host

IIOF2

Used internally by the SMT6025 to signal mailbox interrupts

to the DSP.

Table 1 - Initial state of the IIOF lines when the SMT6025 starts up.

8.4 The PCI bridge chip

The bridge chip forms the link between the host and the carrier board. It

connects the local bus on the carrier board with the PCI bus of the host and

provides apertures that allow the local bus access to the PCI bus. These

apertures act like windows through which the local bus can access data on the

PCI bus.

The internal PCI bridge registers are mapped in BAR0, allowing access by both

the local bus (DSP side) and the PCI bus (host side). Contained in the bridge

chip are the 16 x 8-bit mailbox registers (Section 14).

The bridge chip provides a local bus interrupt line (LINT) as well as a PCI bus

interrupt line (IntA). These interrupt lines allow both the host and the DSP to

interrupt each other.

More information about the bridge chip can be found at

User Manual (QCF42); Version 2.9, 22/02/02; © Sundance Multiprocessor Technology Ltd. 2002