5data registers – Measurement Computing CIO-DO48H User Manual

Page 11

5

DATA REGISTERS

Each CIO-DOxxH is composed of parallel output chips. Each address contains one

latch and one buffer controlling eight output pins. The ports are arranged in sets of

3, with an intervening NA (not used) address area. This scheme allows

compatibility with software written to control 82C55 based boards when the 82C55

is used as all outputs. On those boards every fourth address contains a control

register.

The first address, or BASE ADDRESS 0 , is determined by setting a bank of

switches on the board.

The data registers and their output function are listed on Table 5-1. Each register

has eight output bits. Thus:

CIO-DO48H uses registers 0 to 6 (six registers x 8 bits = 48; skip registers 3 &7)

CIO-DO96H uses registers 0 to 14 (12 registers x 8 bits = 96; skip four registers.)

CIO-DO192H uses registers 0 to 30 (24 registers x 8 bits = 192; skip eight

registers.)

To write a control data to an output register, the individual bits must be set to 0 or 1

then combined to form a Byte.

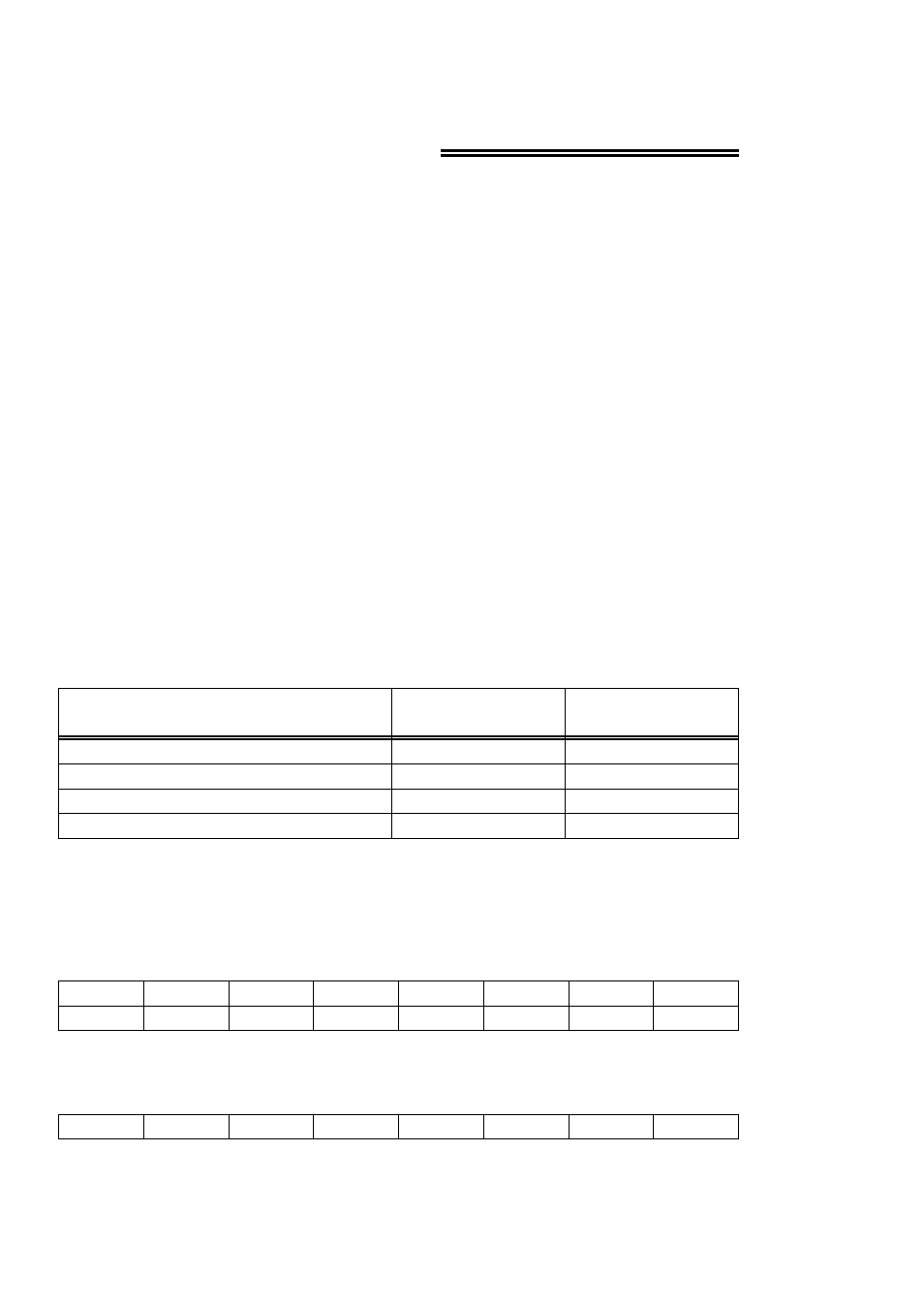

Table 5-1. Data Register Address Summary - All Board Versions

None (skip)

None

BASE +3, 7, 11, 15, 19, 23, 27, 31

Port C Output

None

BASE +2, 6, 10, 14, 18, 22, 26, 30

Port B Output

None

BASE +1, 5, 9, 13, 17, 21, 25, 29

Port A Output

None

BASE +0, 4, 8, 12, 16, 20, 24, 28

WRITE

FUNCTION

READ

ADDRESSES

The port identities (A, B, and C) repeat for each set of 24 digital output lines, so the

CIO-DO48 has two sets of ports, the DO96 has four and the DO192 has eight.

PORT A DATA

BASE ADDRESS + 0 (See Table 5-1 for remaining addresses.)

A0

A1

A2

A3

A4

A5

A6

A7

0

1

2

3

4

5

6

7

PORT B DATA

BASE ADDRESS + 1 (See Table 5-1 for remaining addresses.)

0

1

2

3

4

5

6

7

7